Question: To be completed in System Verilog EEL 4768 Spring 2018 Computer Architecture and organization Display Decoder Lab # 5 Introduction Many digital devices use seven-sepment

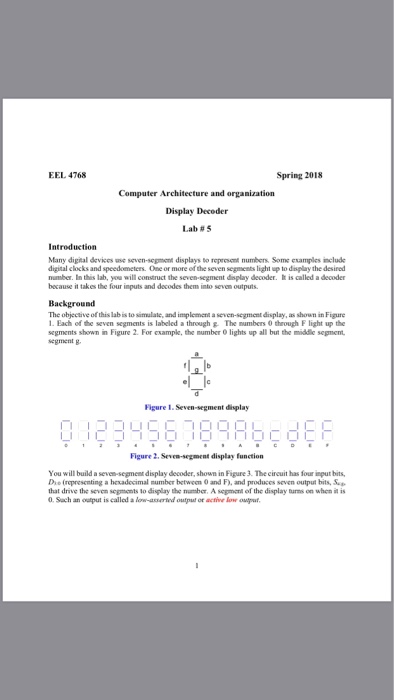

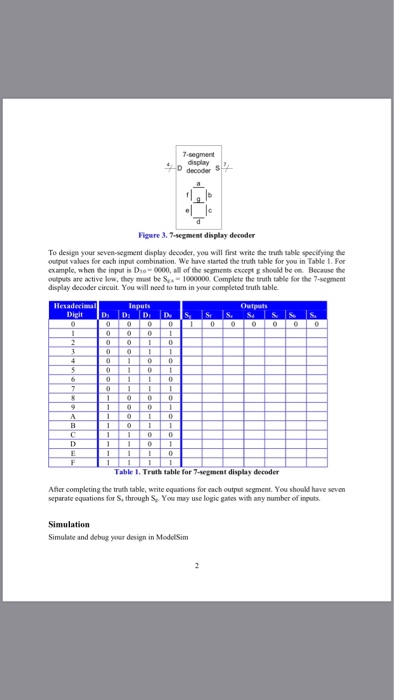

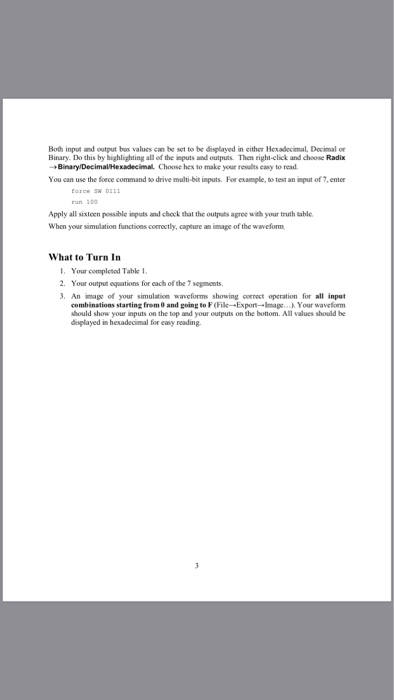

EEL 4768 Spring 2018 Computer Architecture and organization Display Decoder Lab # 5 Introduction Many digital devices use seven-sepment displays to reprosnt numbers Some examples include digital clocks and speedometers. Ose or more ef the seven segments light up to display the desired mumber. In this lab, you will construct the seven-segment display decoder. I is called a decoder because it takes the four inputs and decodes them into seven outputs Background The objective of this lab is to simulale, and implement a seven-sgment display, as shown in Figure 1. Each of the seven segments is labeled a through&The numbers 0 through F light up the segments shown in Figure 2. For exampke, the mumber 0 lights up all but the middle sepment segment g Figure 1. Seven-segment display 123458 1838bEdEF Figure 2. Seven-segment display function You will build a seven-segment display decoder, shown in Figure 3. The circuit has four input bits, Dhe (ropresenting a hexadecimal mumber betwen 0 and F), and produces seven output bits, Sa that drive the seven sepments to display the number. A segment of the display turms on when it is 0. Sach an output is called a low-aserind output or actine low owaf

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts