Question: TOPIC : Computer Architecture- Pipelining I do not need detailed work for this one, Give me the correct answers in shortcut 55 min time Assume

TOPIC : Computer Architecture- Pipelining

I do not need detailed work for this one, Give me the correct answers in shortcut

55 min time

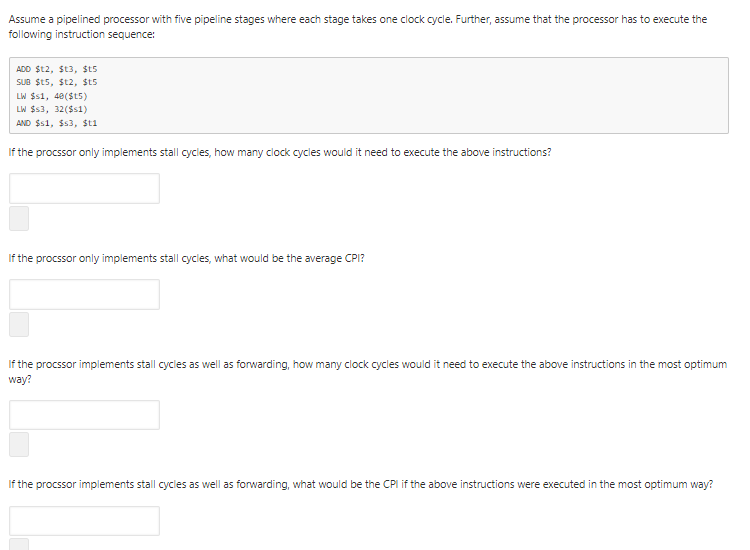

Assume a pipelined processor with five pipeline stages where each stage takes one clock cycle. Further, assume that the processor has to execute the following instruction sequence: ADO $12, $t3, $15 SUB $ts, St2, St5 LW $51, 40($15) LW $53, 32($51) AND $si, $s3, $t1 If the procssor only implements stall cycles, how many clock cycles would it need to execute the above instructions? If the procssor only implements stall cycles, what would be the average CPI? If the procssor implements stall cycles as well as forwarding, how many clock cycles would it need to execute the above instructions in the most optimum way? If the procssor implements stall cycles as well as forwarding, what would be the CP if the above instructions were executed in the most optimum way

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts