Question: Use the Verilog model in example 5.10 on page 207 to create a behavioral model for problem 5.23. Refer to the test-bench example for example

Use the Verilog model in example 5.10 on page 207 to create a behavioral model for problem 5.23. Refer to the test-bench example for example 5.9 on page 206 for how to test your model.

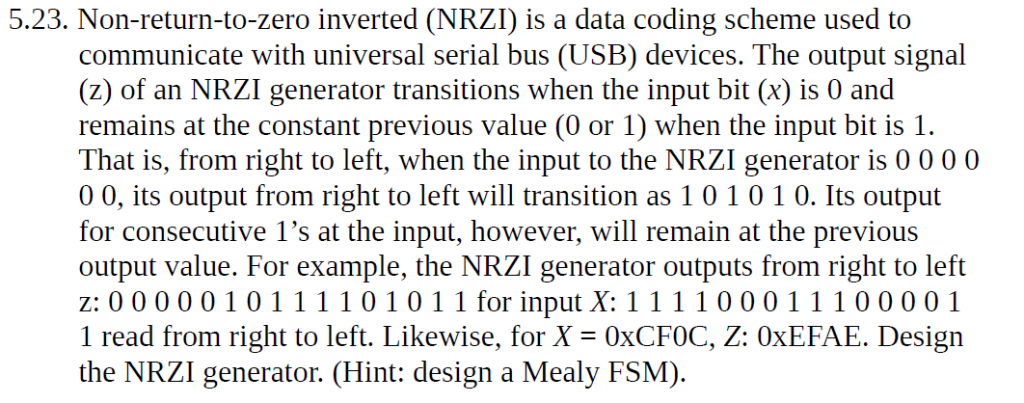

5.23. Non-return-to-zero inverted (NRZI) is a data coding scheme used to communicate with universal serial bus (USB) devices. The output signal (z) of an NRZI generator transitions when the input bit (x) is 0 and remains at the constant previous value (0 or 1) when the input bit is 1. That is, from right to left, when the input to the NRZI generator is 0 0 00 0 0, its output from right to left will transition as 10 10 10. Its output for consecutive 1's at the input, however, will remain at the previous output value. For example, the NRZI generator outputs from right to left : 0 0 0 0 0 1 0 1 1 1 1 0 1 0 1 1 for input X: 1 1 1 1 0 0 0 1 1 1 0 0 0 0 1 1 read from right to left. Likewise, for X- 0xCFOC, Z: OxEFAE. Design the NRZI generator. (Hint: design a Mealy FSM) 5.23. Non-return-to-zero inverted (NRZI) is a data coding scheme used to communicate with universal serial bus (USB) devices. The output signal (z) of an NRZI generator transitions when the input bit (x) is 0 and remains at the constant previous value (0 or 1) when the input bit is 1. That is, from right to left, when the input to the NRZI generator is 0 0 00 0 0, its output from right to left will transition as 10 10 10. Its output for consecutive 1's at the input, however, will remain at the previous output value. For example, the NRZI generator outputs from right to left : 0 0 0 0 0 1 0 1 1 1 1 0 1 0 1 1 for input X: 1 1 1 1 0 0 0 1 1 1 0 0 0 0 1 1 read from right to left. Likewise, for X- 0xCFOC, Z: OxEFAE. Design the NRZI generator. (Hint: design a Mealy FSM)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts