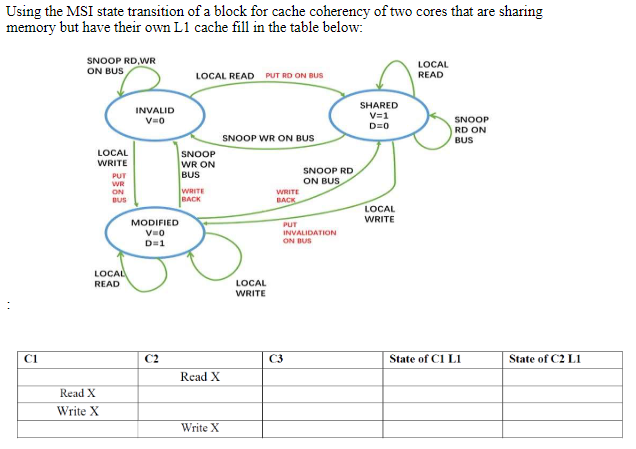

Question: Using the MSI state transition of a block for cache coherency of two cores that are sharing memory but have their own L1 cache fill

Using the MSI state transition of a block for cache coherency of two cores that are sharing memory but have their own L1 cache fill in the table below: SNOOP RDWR ON BUS LOCAL READ PUT RD ON BUS LOCAL READ INVALID Veo SHARED V=1 D=0 SNOOP RD ON BUS SNOOP WR ON BUS LOCAL WRITE PUT WR BUS SNOOP WR ON BUS WRITE BACK SNOOP RD ON BUS WRITE BACK ON LOCAL WRITE PUT MODIFIED Voo D=1 INVALIDATION ON BUS LOCAL READ LOCAL WRITE C2 C3 State of CILI State of C2 L1 Read X Read X Write X Write X Using the MSI state transition of a block for cache coherency of two cores that are sharing memory but have their own L1 cache fill in the table below: SNOOP RDWR ON BUS LOCAL READ PUT RD ON BUS LOCAL READ INVALID Veo SHARED V=1 D=0 SNOOP RD ON BUS SNOOP WR ON BUS LOCAL WRITE PUT WR BUS SNOOP WR ON BUS WRITE BACK SNOOP RD ON BUS WRITE BACK ON LOCAL WRITE PUT MODIFIED Voo D=1 INVALIDATION ON BUS LOCAL READ LOCAL WRITE C2 C3 State of CILI State of C2 L1 Read X Read X Write X Write X

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts