Question: Using VHDL, design an 8-to-3 priority encoder. The input is X: bit_vector(7 downto 0) . Outputs are Y: bit_vector(2 downto 0) and V: bit; V

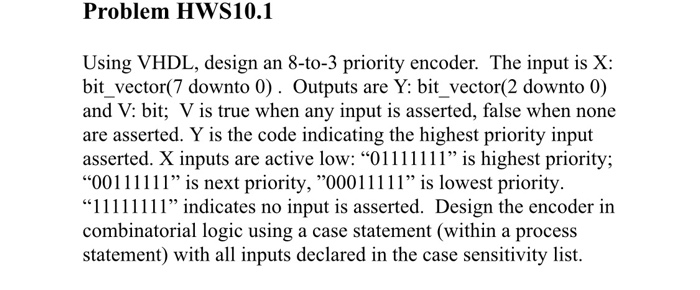

Problem HWS10.1 Using VHDL, design an 8-to-3 priority encoder. The input is X: bit_vector(7 downto 0). Outputs are Y: bit_vector(2 downto 0) and V: bit; V is true when any input is asserted, false when none are asserted. Y is the code indicating the highest priority input asserted. X inputs are active low: "01111111 is highest priority; "00111111" is next priority, "00011111" is lowest priority. 11111111 indicates no input is asserted. Design the encoder in combinatorial logic using a case statement (within a process statement) with all inputs declared in the case sensitivity list

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts