Question: void foo(int a, int b, float x,float y, float , int* iresult, float fresult) { int templ =.*b; terpl + b; float temp2 = x

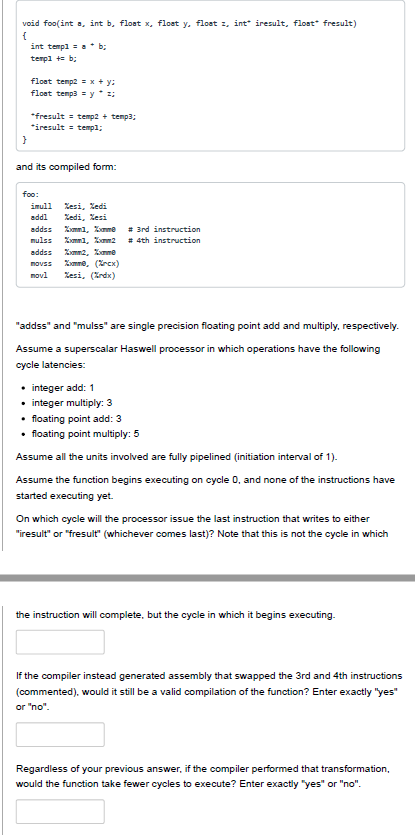

void foo(int a, int b, float x,float y, float , int* iresult, float fresult) { int templ =.*b; terpl + b; float temp2 = x + y: float temp3 = y 3; *fresult = temp2 + temp]; *iresult = tempa: } and its compiled form: foo: imull Kesi, Kedi addl Kedi, Sesi addss El, came mulss addss moss mm, (Erex) movl Kesi, (Xdx) # 3rd instruction # 4th instruction "addss" and "mulss" are single precision floating point add and multiply, respectively. Assume a superscalar Haswell processor in which operations have the following cycle latencies: integer add: 1 integer multiply: 3 . floating point add: 3 floating point multiply: 5 Assume all the units involved are fully pipelined (initiation interval of 1). Assume the function begins executing on cycle 0, and none of the instructions have started executing yet. On which cycle will the processor issue the last instruction that writes to either "iresult" or "fresult" (whichever comes last)? Note that this is not the cycle in which the instruction will complete, but the cycle in which it begins executing. If the compiler instead generated assembly that swapped the 3rd and 4th instructions (commented), would it still be a valid compilation of the function? Enter exactly "yes" or "no". Regardless of your previous answer, if the compiler performed that transformation, would the function take fewer cycles to execute? Enter exactly "yes" or "no". void foo(int a, int b, float x,float y, float , int* iresult, float fresult) { int templ =.*b; terpl + b; float temp2 = x + y: float temp3 = y 3; *fresult = temp2 + temp]; *iresult = tempa: } and its compiled form: foo: imull Kesi, Kedi addl Kedi, Sesi addss El, came mulss addss moss mm, (Erex) movl Kesi, (Xdx) # 3rd instruction # 4th instruction "addss" and "mulss" are single precision floating point add and multiply, respectively. Assume a superscalar Haswell processor in which operations have the following cycle latencies: integer add: 1 integer multiply: 3 . floating point add: 3 floating point multiply: 5 Assume all the units involved are fully pipelined (initiation interval of 1). Assume the function begins executing on cycle 0, and none of the instructions have started executing yet. On which cycle will the processor issue the last instruction that writes to either "iresult" or "fresult" (whichever comes last)? Note that this is not the cycle in which the instruction will complete, but the cycle in which it begins executing. If the compiler instead generated assembly that swapped the 3rd and 4th instructions (commented), would it still be a valid compilation of the function? Enter exactly "yes" or "no". Regardless of your previous answer, if the compiler performed that transformation, would the function take fewer cycles to execute? Enter exactly "yes" or "no

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts