Question: We have a synchronous counter with counting sequence is Q [ 2 : 0 ] = 0 0 0 , 0 0 1 , 0

We have a synchronous counter with counting sequence is : and wrapping back to Show the block diagram with the register, the adderincrementer the load muxes, and the decoder logic. pt

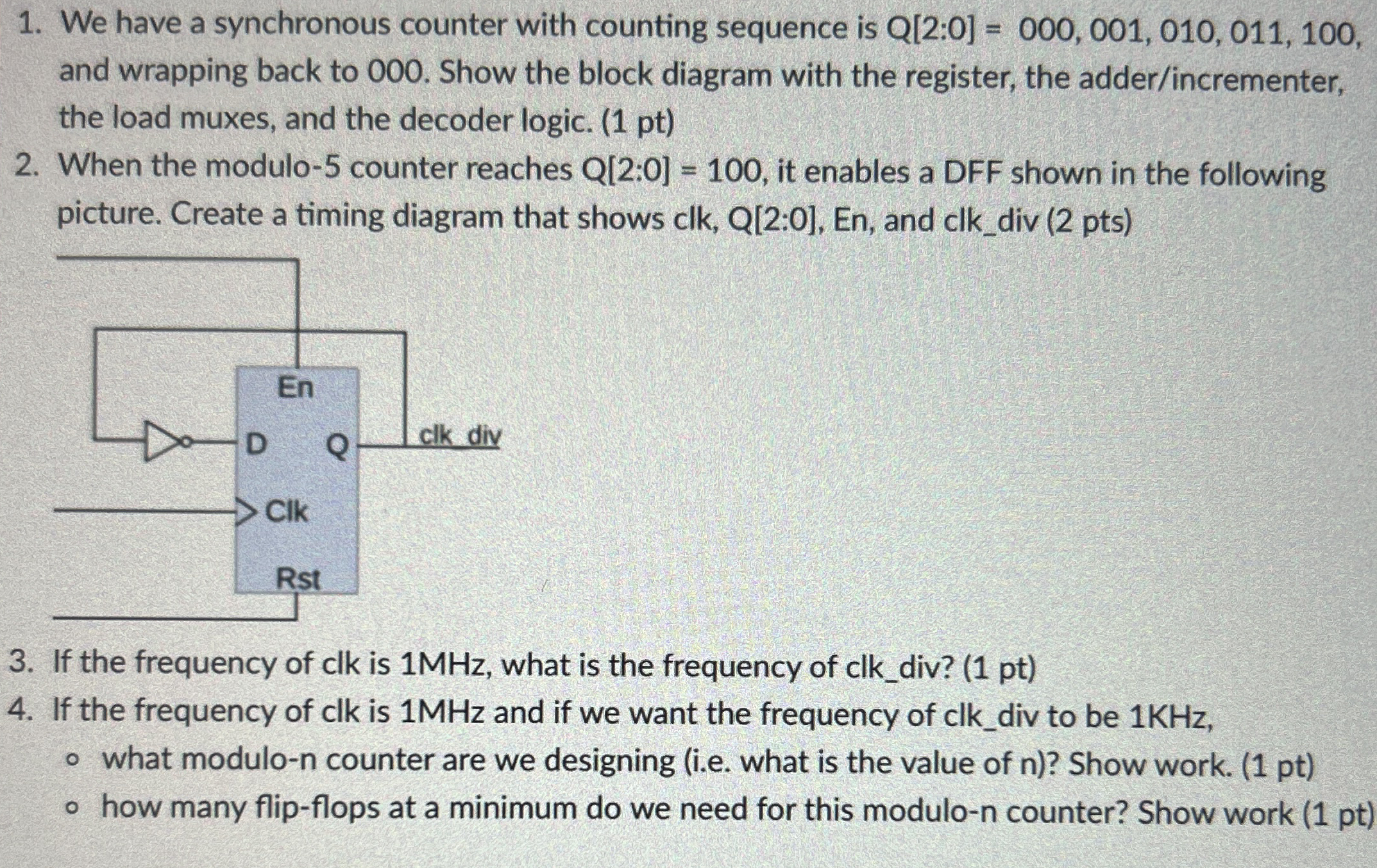

When the modulo counter reaches : it enables a DFF shown in the following picture. Create a timing diagram that shows clk Q: En and clkdiv pts

If the frequency of clk is MHz what is the frequency of clkdiv? pt

If the frequency of clk is MHz and if we want the frequency of clkdiv to be KHz

what modulon counter are we designing ie what is the value of n Show work. pt

how many flipflops at a minimum do we need for this modulon counter? Show work pt

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock