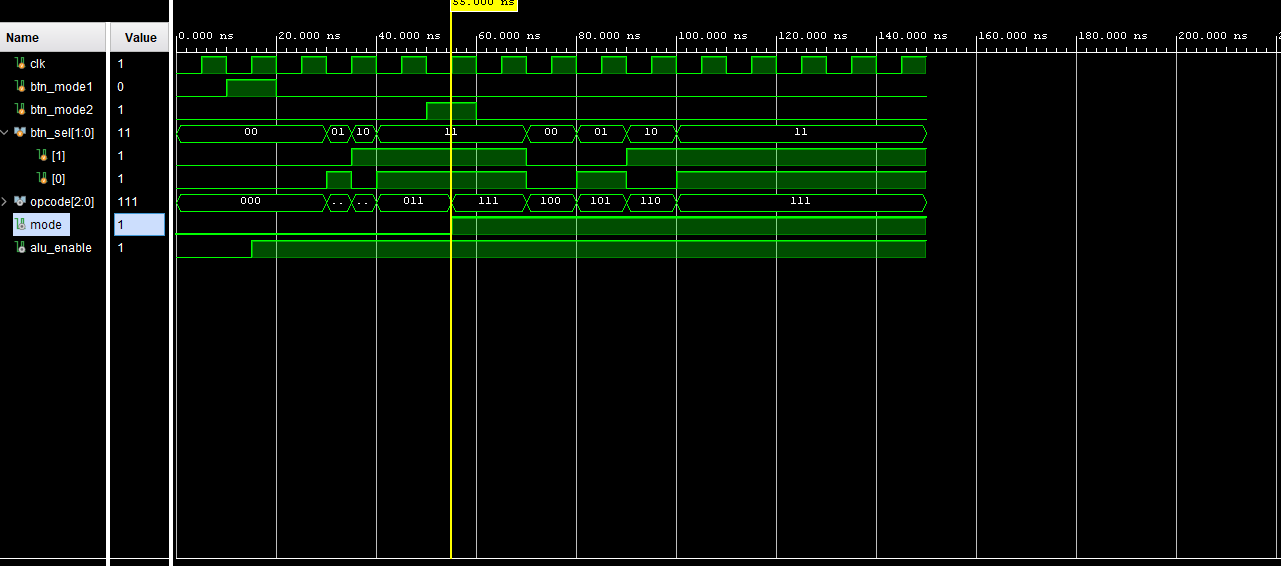

Question: why is the btn _ sel 1 1 staying while the mode switch and how can you get rid of that so it go to

why is the btnsel staying while the mode switch and how can you get rid of that so it go to the second mode and string to

module calculatorfsm

input clk

input btnmode

input btnmode

input : btnsel,

output reg : opcode,

output reg mode,

output reg aluenable

;

localparam MODEb; Arithmetic operations

localparam MODEb; Bitwise operations

reg currentmode;

reg btnmodelast, btnmodelast;

reg : btnselinternal;

Detect mode switch and reset btnsel

always @posedge clk begin

if btnmode && btnmodelast begin

currentmode MODE;

btnselinternal b; Reset to default operation

end else if btnmode && btnmodelast begin

currentmode MODE;

btnselinternal b; Reset to default operation

end else begin

btnselinternal btnsel; Retain btnsel

end

btnmodelast btnmode;

btnmodelast btnmode;

end

always @ begin

aluenable ; Default disable ALU

case currentmode

MODE: begin

mode ; Arithmetic Mode

case btnsel

b: opcode b; Addition

b: opcode b; Subtraction

b: opcode b; Multiplication

b: opcode b; Division

default: opcode b; Default to Addition

endcase

aluenable ;

end

MODE: begin

mode ; Bitwise Mode

case btnsel

b: opcode b; AND

b: opcode b; OR

b: opcode b; Shift Left

b: opcode b; Shift Right

default: opcode b; Default to AND

endcase

aluenable ;

end

default: begin

mode ;

opcode b;

aluenable ;

end

endcase

end

endmodule

timescale ns ps

module calculatorfsmtb;

reg clk btnmode btnmode;

reg : btnsel;

wire : opcode;

wire mode;

wire aluenable;

calculatorfsm uut

clkclk

btnmodebtnmode

btnmodebtnmode

btnselbtnsel

opcodeopcode

modemode

aluenablealuenable

;

Clock generation

initial begin

clk ;

forever # clk ~clk; ns clock period

end

Test sequence

initial begin

Initialize inputs

btnmode;

btnmode;

btnsel b;

Wait for some time before starting

#;

Step through all operations in Arithmetic mode

btnmode; # btnmode; Select Arithmetic mode

# btnsel b; Addition

# btnsel b; Subtraction

# btnsel b; Multiplication

# btnsel b; Division

#;

Step through all operations in Bitwise mode

btnmode; # btnmode; Select Bitwise mode

# btnsel b; AND

# btnsel b; OR

# btnsel b; Shift Left

# btnsel b; Shift Right

End simulation

# $finish;

end

endmodule

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock