Question: Write a Verilog program which implements and tests a four element cache with four bit memory addresses in three configurations: 1. Direct mapped, 2. Two-way

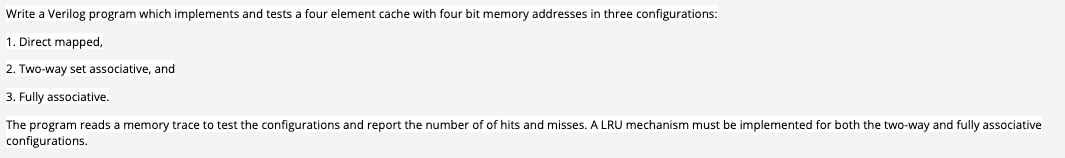

Write a Verilog program which implements and tests a four element cache with four bit memory addresses in three configurations: 1. Direct mapped, 2. Two-way set associative, and 3. Fully associative. The program reads a memory trace to test the configurations and report the number of of hits and misses. A LRU mechanism must be implemented for both the two-way and fully associative configurations. Write a Verilog program which implements and tests a four element cache with four bit memory addresses in three configurations: 1. Direct mapped, 2. Two-way set associative, and 3. Fully associative. The program reads a memory trace to test the configurations and report the number of of hits and misses. A LRU mechanism must be implemented for both the two-way and fully associative configurations

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts