Question: write in Verilog code Problem 1. Latch implementation: 1) Using always statement, write a transparent latch having active high enable, and active low set and

write in Verilog code

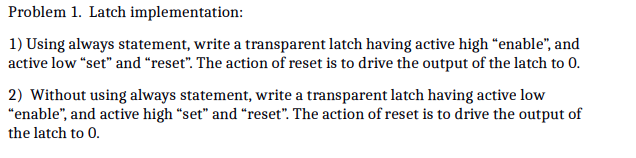

Problem 1. Latch implementation: 1) Using always statement, write a transparent latch having active high "enable", and active low "set" and "reset". The action of reset is to drive the output of the latch to 0. 2) Without using always statement, write a transparent latch having active low "enable" and active high "set" and "reset". The action of reset is to drive the output of the latch to 0. Problem 1. Latch implementation: 1) Using always statement, write a transparent latch having active high "enable", and active low "set" and "reset". The action of reset is to drive the output of the latch to 0. 2) Without using always statement, write a transparent latch having active low "enable" and active high "set" and "reset". The action of reset is to drive the output of the latch to 0

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts