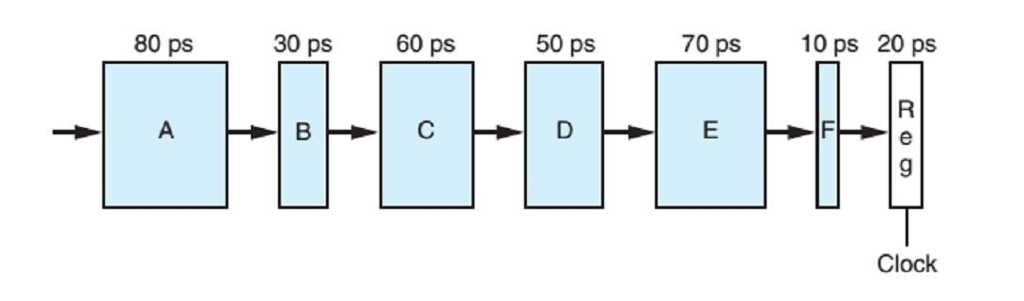

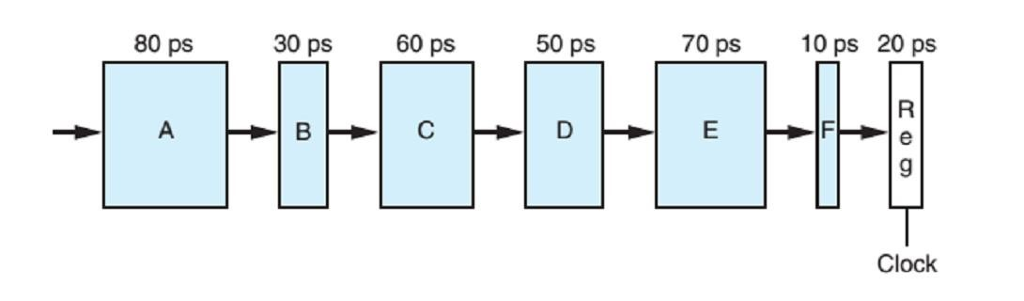

Question: You are given the following processor architecture with six stages A-F. Currently, the processor is not pipelined i.e. it is a single stage processor and

You are given the following processor architecture with six stages A-F. Currently, the processor is not pipelined i.e. it is a single stage processor and there are no Inter-Stage Registers (ISRs) except one at the end to store the output.

Assumptions:

Say you had the ability to insert any number of ISRs in the design to pipeline it.

Each register will introduce a delay of 20 ps. (1 ps = 10-12 s)

Questions

Where would you insert the minimal number of ISRs to maximize throughput? Indicate the insertion points in the diagram. Calculate the throughput and latency of your optimized pipeline.

Repeat the above question with the following additional assumption:

a. Assume that a throughput increase smaller than (109 per sec) is not cost beneficial, i.e. if introducing another ISR results in a throughput increase 9 per sec, do not insert another ISR.

50 ps 70 ps 10 ps 20 ps 80 ps 30 ps 60 ps Clock 50 ps 70 ps 10 ps 20 ps 80 ps 30 ps 60 ps Clock

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts