Question: Parity self-checking checker Achecker is intended to detect errors on an input parity code having 4 bits, a, b, C and d (3 bits of

Parity self-checking checker Achecker is intended to detect errors on an input parity code having 4 bits,

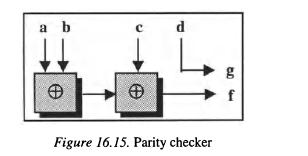

a, b, C and d (3 bits of data plus one parity bit); it delivers two outputsf and g coded with a l-out-of-2 code (01 and 10 are the codewords). We realize this checker with two XOR gates as shown in Figure 16.15.

1. Is this circuit a self-checking checker? Give an example of a minimal sub-set of vectors of the parity code that ensures the self-testing property.

2. Show that this circuit is no Ion ger self-testing if all the input vectors of the parity code are not applied.

3. Does a permutation of the input variables

(a,

b, c,

d) have an influence on the property of the previous question?

b d 0 Figure 16.15. Parity checker g

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts