The following fragment of code is to be executed on two different superscalar processors. The processors have

Question:

The following fragment of code is to be executed on two different superscalar processors. The processors have two integer units and two load/store units (i.e., up to two memory accesses and two integer operations can be executed concurrently. The fetch window is eight instructions. Show how it would be executed, cycle-by-cycle, on the following.

a. Superscalar with in-order issue and in-order execution.

b. Superscalar with out-of-order issue and out-oforder execution.

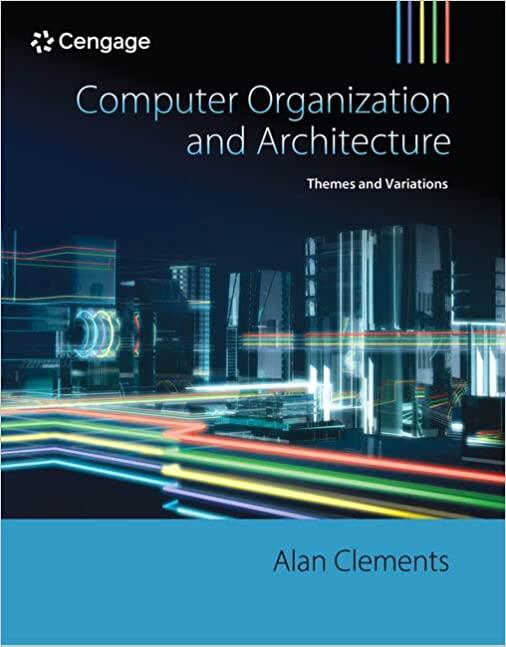

![LDR ADD STR ADD ADD LDR ADD ADD ADD STR ADD SUBS r3, [ro] ro, ro, #4 r3, [16] r6, r6, #4 r8, r8, r3 r4, [rl]](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1705/7/6/9/22065abf9041dcf11705769219938.jpg)

Assume that the latency for each instruction is one cycle, except for a load which is two cycles. Assume that the multiply operation has a latency of two cycles and that the multiplier cannot be reused until the previous instruction has been completed.

Step by Step Answer:

Computer Organization And Architecture Themes And Variations

ISBN: 9781111987046

1st Edition

Authors: Alan Clements