Question: When an interrupt is detected, the Status register is saved and all but the highest priority interrupt is disabled. Why are low-priority interrupts disabled? Why

When an interrupt is detected, the Status register is saved and all but the highest priority interrupt is disabled. Why are low-priority interrupts disabled? Why is the status register saved prior to disabling interrupts?

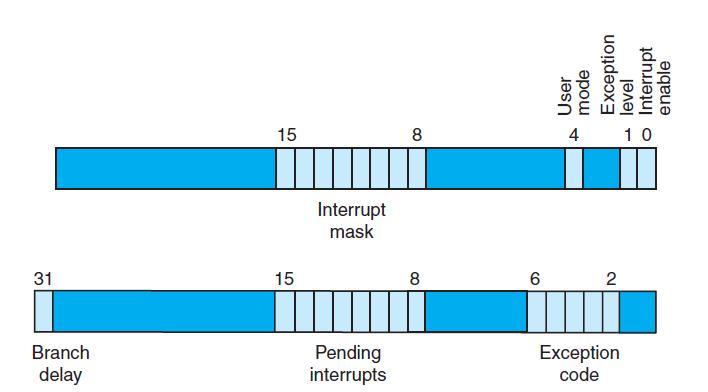

Section 6.6 defines an eight-step process for handling interrupts. The Cause and Status registers together provide information on the cause of the interrupt and the status of the interrupt handling system. Explore interrupt handling by answering the questions about the following combinations of interrupts.

Data From Section 6.6

1. Logically AND the pending interrupt field and the interrupt mask field to see which enabled interrupts could be the culprit. Copies are made of these two registers using the mfc0 instruction.

2. Select the higher priority of these interrupts. The software convention is that the leftmost is the highest priority. 3. Save the interrupt mask field of the Status register.

3. Save the interrupt mask field of the Status register.

4. Change the interrupt mask field to disable all interrupts of equal or lower priority.

5. Save the processor state needed to handle the interrupt.

6. To allow higher-priority interrupts, set the interrupt enable bit of the Cause register to 1.

7. Call the appropriate interrupt routine.

8. Before restoring state, set the interrupt enable bit of the Cause register to 0. This allows you to restore the interrupt mask field.

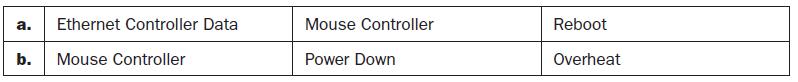

a. Ethernet Controller Data b. Mouse Controller Mouse Controller Power Down Reboot Overheat

Step by Step Solution

3.51 Rating (154 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts