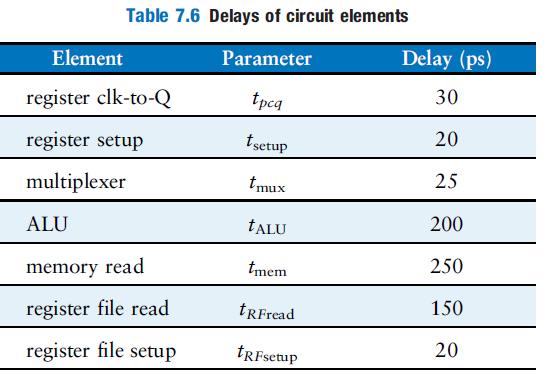

Question: Consider the delays from Table 7.6 and Example 7.10. Now suppose that the ALU was 20% faster. Would the cycle time of the pipelined MIPS

Consider the delays from Table 7.6 and Example 7.10. Now suppose that the ALU was 20% faster. Would the cycle time of the pipelined MIPS processor change? What if the ALU were 20% slower?

Table 7.6 Delays of circuit elements Element Parameter Delay (ps) register clk-to-Q tpeg 30 register setup tsetup 20 multiplexer 25 'mux ALU TALU 200 memory read tmem 250 register file read trFread 150 register file setup tRFsetup 20

Step by Step Solution

3.48 Rating (161 Votes )

There are 3 Steps involved in it

Increasing the ALU delay by 20 from 200 ps to 24... View full answer

Get step-by-step solutions from verified subject matter experts