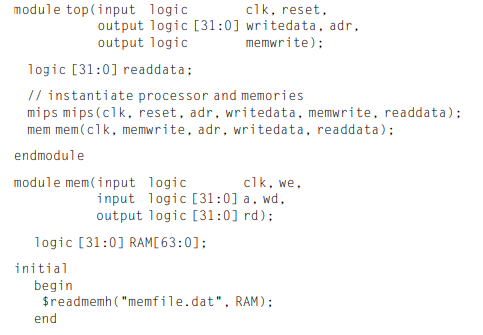

Digital Design and Computer Architecture 2nd edition David Harris, Sarah Harris - Solutions

Discover comprehensive resources for "Digital Design and Computer Architecture, 2nd Edition" by David Harris and Sarah Harris. Access the online answers key and solutions manual with step-by-step answers to enhance your understanding. Dive into solved problems and chapter solutions available in a solutions PDF format. Explore the extensive test bank and instructor manual for thorough preparation. This textbook is a valuable resource for anyone seeking detailed questions and answers. Enjoy the convenience of a free download with complete chapter solutions and an instructor manual to further aid your studies.

![]()

![]() New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

![]()

![]()