Question: Repeat Exercise 15.22, instead using flip-flop specification B and a 2 ns clock. Data in Exercise 15.22, Calculate the maximum allowable clock skew in Figure

Repeat Exercise 15.22, instead using flip-flop specification B and a 2 ns clock.

Data in Exercise 15.22,

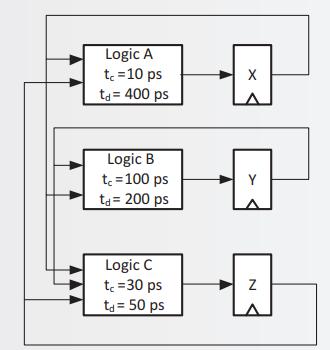

Calculate the maximum allowable clock skew in Figure 15.19. Indicate between which pair of flip-flops the skew occurs and whether it will trigger a setup or hold violation. Use flip-flop specification A and a 2 ns clock. You may want to enumerate all possible paths and write the setup and hold equations.

Data in Figure 15.19.

Step by Step Solution

3.39 Rating (165 Votes )

There are 3 Steps involved in it

Using flipflop specification B and a 2 ns clock the maximum allowable clock skew can be calculated b... View full answer

Get step-by-step solutions from verified subject matter experts