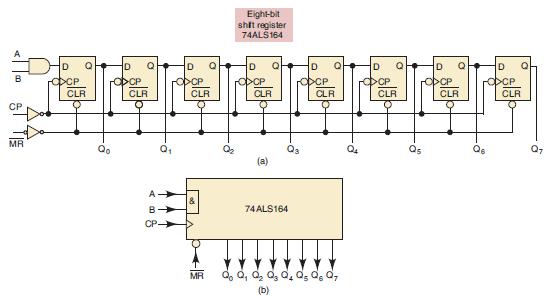

Figure 7-73 shows an eight-bit shift register that could be used to delay a signal by 1

Question:

Figure 7-73 shows an eight-bit shift register that could be used to delay a signal by 1 to 8 clock periods. Show how to wire a 74151 to this shift register in order to select the desired Q output and indicate the logic level necessary on the select inputs to provide a delay of 6 × Tclk.

Figure 7-73

Transcribed Image Text:

A B CP MR D rCDCP Q CLR Qo ID ODCP Q CLR Q₁ D Q CP CLR MR ♂ Eight-bit shit register 74ALS164 D >CP 20₁ CLR (a) Q 74ALS164 (b) D PODCP Q₂ Q CLR Q5 Qe Q7 P. D CDCP Q CLR Qs Q D ODCP CLR D ODCP CLR Q₂ Q7

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 33% (3 reviews)

Answered By

Ashington Waweru

I am a lecturer, research writer and also a qualified financial analyst and accountant. I am qualified and articulate in many disciplines including English, Accounting, Finance, Quantitative spreadsheet analysis, Economics, and Statistics. I am an expert with sixteen years of experience in online industry-related work. I have a master's in business administration and a bachelor’s degree in education, accounting, and economics options.

I am a writer and proofreading expert with sixteen years of experience in online writing, proofreading, and text editing. I have vast knowledge and experience in writing techniques and styles such as APA, ASA, MLA, Chicago, Turabian, IEEE, and many others.

I am also an online blogger and research writer with sixteen years of writing and proofreading articles and reports. I have written many scripts and articles for blogs, and I also specialize in search engine

I have sixteen years of experience in Excel data entry, Excel data analysis, R-studio quantitative analysis, SPSS quantitative analysis, research writing, and proofreading articles and reports. I will deliver the highest quality online and offline Excel, R, SPSS, and other spreadsheet solutions within your operational deadlines. I have also compiled many original Excel quantitative and text spreadsheets which solve client’s problems in my research writing career.

I have extensive enterprise resource planning accounting, financial modeling, financial reporting, and company analysis: customer relationship management, enterprise resource planning, financial accounting projects, and corporate finance.

I am articulate in psychology, engineering, nursing, counseling, project management, accounting, finance, quantitative spreadsheet analysis, statistical and economic analysis, among many other industry fields and academic disciplines. I work to solve problems and provide accurate and credible solutions and research reports in all industries in the global economy.

I have taught and conducted masters and Ph.D. thesis research for specialists in Quantitative finance, Financial Accounting, Actuarial science, Macroeconomics, Microeconomics, Risk Management, Managerial Economics, Engineering Economics, Financial economics, Taxation and many other disciplines including water engineering, psychology, e-commerce, mechanical engineering, leadership and many others.

I have developed many courses on online websites like Teachable and Thinkific. I also developed an accounting reporting automation software project for Utafiti sacco located at ILRI Uthiru Kenya when I was working there in year 2001.

I am a mature, self-motivated worker who delivers high-quality, on-time reports which solve client’s problems accurately.

I have written many academic and professional industry research papers and tutored many clients from college to university undergraduate, master's and Ph.D. students, and corporate professionals. I anticipate your hiring me.

I know I will deliver the highest quality work you will find anywhere to award me your project work. Please note that I am looking for a long-term work relationship with you. I look forward to you delivering the best service to you.

3.00+

2+ Reviews

10+ Question Solved

Related Book For

Digital Systems Principles And Application

ISBN: 9780134220130

12th Edition

Authors: Ronald Tocci, Neal Widmer, Gregory Moss

Question Posted:

Students also viewed these Computer science questions

-

A study was conducted on a sample of 53 patients presenting with prostate cancer who had also undergone a laparotomy to ascertain the extent of nodal involvement (Collett 1991). The result of the...

-

On June 23, 2018, in Thailand, a group of 12 boys aged between 11 and 17 from the local football team, named the Wild Boars, and their 23-year-old assistant coach entered the Tham Luang cave. Tham...

-

Managing Scope Changes Case Study Scope changes on a project can occur regardless of how well the project is planned or executed. Scope changes can be the result of something that was omitted during...

-

Consider thedeadlock situation that could occur in the dining-philosophers problem when the philosophers obtain the chopsticks one at a time. Discuss how the four necessary conditions for deadlock...

-

In 1969 a deed for land in Pitt County was executed and delivered by Joel and Louisa Tyson unto M. H. Jackson and wife Maggie Jackson, for and during the term of their natural lives and after their...

-

A professor in the School of Business in a university polled a dozen colleagues about the number of professional meetings professors attended in the past five years (X) and the number of papers...

-

Why is it advisable to obtain a written confession from the subject of an investigation?

-

Assume that your firm, Daulton & Weed, CPAs, has been approached by a Tempest, a golf ball manufacturer to attest to the average drive distance that Tempests new GOFAR ball can be driven. Tempest has...

-

13. An analyst is valuing Red Inc. common stock using the dividend discount model. The company plans to start paying dividends with its first dividend of $3.25 per share occurring next year. To...

-

(a) Use the idea from Problem 9-29 to arrange several 74151 1-of-8 multiplexers to form a 1-of-64 multiplexer. (b) Use a Quartus II megafunction to create a 1-of-2 MUX, a 1-of-4 MUX, and a 1-of-8...

-

The timing diagram in Figure 9-77 is applied to Figure 9-19. Draw the output waveform Z. Figure 9-77 Figure 9-19 S th T

-

Multiple Choice Questions: 1. Money's principal role is to serve as? a. A standard for credit transactions. b. A medium of exchange. c. A standard for making bank loans. d. A standard for the real...

-

Below are three options for the opening section of a resume. Match them with the appropriate word(s). Group of answer choices Summary -- Recent MBA graduate with three semesters of intern experience...

-

Proponents of absorption costing argue that Blank______. Multiple select question. fixed overhead costs will be incurred every period, regardless of production levels only costs that will not be...

-

Which type of bond is suitable for an investor seeking currency diversification? Foreign bond Foreign-pay bond Eurobond All of the above

-

Upon reviewing Coca-Cola's income statement and balance sheet, several performance indicators emerge. Firstly, analyzing revenue trends from the income statement offers insights into the company's...

-

Critically discuss Performance Management as an integrated 'strategic' process. You must also comment on the main HR tools used in performance management. Line managers manage employees and are...

-

What is the theory of constraints?

-

In the circuit shown in Figure 4, a battery supplies a constant voltage of 40 V, the inductance is 2 H, the resistance is 10, and l(0) = 0. (a) Find l(t). (b) Find the current after 0.1s.

-

The pulley in Fig. 936 has radius 0.160 m and moment of inertia 0.480 kg m2. The rope does not slip on the pulley rim. Use energy methods to calculate the speed of the 4.00-kg block just before it...

-

You hang a thin hoop with radius R over a nail at the rim of the hoop. You displace it to the side (within the plane of the hoop) through an angle fJ from its equilibrium position and let it go. What...

-

A passenger bus in Zurich, Switzerland, derived its motive power from the energy stored in a large flywheel. The wheel was brought up to speed periodically, when the bus stopped at a station, by an...

-

This year SanCorp had $10 million in sales, $5.2 million in operating costs, and $200,000 in interest expense. It also paid 40 percent of its pre-tax income to the government as income tax expense....

-

what will happen to Miami, Florida if the temperature increase to 1.5C.

-

On March 31, 2021, a farmer knows he will need to sell 15,000 bushels of wheat some time in October 2021. The November wheat futures price is 778.3 cents per bushel. Each wheat futures contract is on...

Study smarter with the SolutionInn App