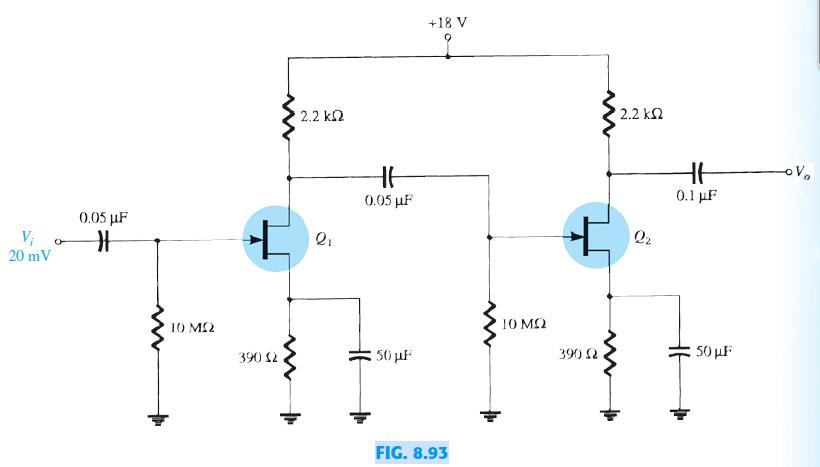

For the JFET cascade amplifier in Fig. 8.93 , calculate the dc bias conditions for the two

Question:

For the JFET cascade amplifier in Fig. 8.93 , calculate the dc bias conditions for the two identical stages, using JFETs with IDSS = 8 mA and VP = -4.5 V.

Transcribed Image Text:

+18 V 2.2 k2 2.2 k2 0.05 µF 0.1 µF 0.05 µF Q2 20 mV 10 M2 10 MQ 390 2 50 µF 390 2 50 µF FIG. 8.93

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 66% (9 reviews)

For the JFET cascade amplifier in Fig 893 calculate the dc bias conditions for the two identical sta...View the full answer

Answered By

Labindao Antoque

I graduated in 2018 with a Bachelor of Science degree in Psychology from Dalubhasaan ng Lungsod ng San Pablo. I tutored students in classes and out of classes. I use a variety of strategies to tutor students that include: lecture, discussions about the subject matter, problem solving examples using the principles of the subject matter being discussed in class , homework assignments that are directed towards reinforcing what we learn in class , and detailed practice problems help students to master a concept. I also do thorough research on Internet resources or textbooks so that I know what students need to learn in order to master what is being taught in class .

0.00

0 Reviews

10+ Question Solved

Related Book For

Electronic Devices And Circuit Theory

ISBN: 9781292025636

11th Edition

Authors: Robert Boylestad, Louis Nashelsky

Question Posted:

Students also viewed these Engineering questions

-

Using IDSS = 9 mA and VP = -3 V for the characteristics of Fig. 6.25, calculate ID at VGS = -1 V using Shockley's equation and compare to the level in Fig. 6.25.

-

For the BJT cascade amplifier of Fig. 5.176, calculate the dc bias voltages and collector current for each stage. +15 V 5.1 kQ 24 k 5.1 k 24 k2 0.5 HF If 0.5 pF - 150 6.2 k2 6.2 kQ 50 uF

-

Using an average value of 2.9 mA for the IDSS of the 2N3797 MOSFET of Fig. 6.34, determine the level of VGS that will result in a maximum drain current of 20 mA if VP = -5 V.

-

Identify each process as endothermic or exothermic and indicate the sign of H. (a) Sweat evaporating from skin (b) Water freezing in a freezer (c) Wood burning in a fire

-

In the United States, say gasoline costs consumers about $2.50 per gallon. In Italy, say it costs consumers about $6 per gallon. What effect does this price differential likely have on a. The size of...

-

1. What type of team was formed here? Was it necessary, in your opinion? 2. Use the team effectiveness model and related information in this chapter to identify the strengths and weaknesses of this...

-

Automobile Injury Insurance Claims. Refer to the description in Exercise 1.5 .We consider \(n=1,340\) bodily injury liability claims from a single state using a 2002 survey conducted by the Insurance...

-

This is the third year audit of Green Lawns. The company has carved out a new market niche on the Web for the delivery of lawn and garden supplies, including links with local companies that provide...

-

Consider the following combinational circuit with 3 inputs a, b, c and two outputs F1 and Fo given by its truth table. a b C Fo F 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 0 0 1 1 0 0 1 1...

-

Where within the Excel spreadsheet and its different menus (under what menu button option) can you find the different functions that will enable you to solve for different time value of money factors?

-

If both JFETs in the cascade amplifier of Fig. 8.93 are changed to those having specifications I DSS = 12 mA and V P = -3 V, calculate the resulting d c bias of each stage. Fig. 8.93 +18 V 2.2 k2 2.2...

-

For the common-gate configuration of Fig. 8.92 : a. Determine A vNL , Z i and Z o . b. Sketch the two-port model of Fig. 5.75 with the parameters determined in part (a) in place. c. Determine A vL...

-

1. The lifetime of a certain brand of tires is normally distributed with mean m = 30,000 miles and standard deviation = 5000 miles. The company has decided to issue a warranty for the tires but does...

-

Explain the role of business process reengineering in various functional strategies.

-

Most organizations can be classified as either ethical or unethical. True or False

-

Explain the linkage that a JIT inventory system provides between the purchasing and production functions. What are the implications for quality?

-

An internationally renowned professor specialising in management accounting has agreed to conduct a one-day seminar at a university for management executives. The Head of the Graduate School...

-

All industries follow the stages of the industry life cycle model. True or False

-

Palmitic acid (hexadecanoic acid) is a saturated 16-carbon fatty acid. How many moles of malonyl-CoA are required for the synthesis of one mole of palmitic acid?

-

Would you use the adjacency matrix structure or the adjacency list structure in each of the following cases? Justify your choice. a. The graph has 10,000 vertices and 20,000 edges, and it is...

-

The efficiency of a gas chromatography column is measured by a parameter called plate height (H, mm) which is related to the gas flow rate (u, mL/min) by the van Deemter equation: H = A + B/u + Cu,...

-

Write each answer with a reasonable number of figures. Find the absolute and percent relative uncertainty for each answer. (a) [12.41 (0.09) 4.16 ( 0.01)] 7.068 2 ( 0.000 4) = ? (b) [3.26 (0.10) ...

-

How many milliliters of 53.4 (0.4) wt% NaOH with a density of 1.52 ( 0.01) g/mL will you need to prepare 2.000 L of 0.169 M NaOH? (b) If the uncertainty in delivering NaOH is [1] 0.01 mL, calculate...

-

In North Carolina, transaction records must be retained for several years. Unset starred question At the conclusion of the transaction, or after all transaction funds held by the broker have been...

-

How has organizational culture been a factor in the success of a business?

-

Your rent is $800 a month, health insurance is $200, food is $1000, clothing budget is $150 (for everyone), electric is $70, gas is $110, cell phone is $100, car insurance is $114 and you spend...

Study smarter with the SolutionInn App