Question: Using behavioral VHDL, design a Moore-type finite state machine that detects input test vector that contains the sequence of ?10?. If the sequence ?10? is

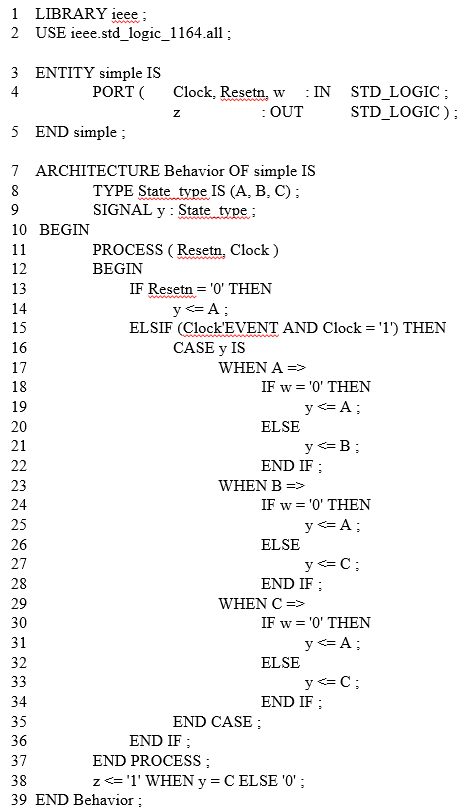

Using behavioral VHDL, design a Moore-type finite state machine that detects input test vector that contains the sequence of ?10?. If the sequence ?10? is detected, the output Z should go high. The input is to be named W, the output is to be named Z, a Clock input is to be used and an active low reset signal (Resetn) should asynchronously reset the machine.

(a) Draw the Moore-type model state diagram for the FSM.

(b) Write the VHDL code to implement the FSM.

We were given code to alter to fit the above question. Please explain the changes for my understanding.

1 LIBRARY ieee; 2 3 ENTITY simple IS 4 PORT ( 5 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 PREZENO27222 23 24 25 26 28 29 30 31 32 33 USE ieee.std_logic_1164.all; 34 35 36 37 BEGIN Clock, Resetn, w Z : OUT END simple; ARCHITECTURE Behavior OF simple IS TYPE State type IS (A, B, C); SIGNAL y: State_type; PROCESS (Resetn, Clock) BEGIN IF Resetn = '0' THEN y

Step by Step Solution

3.49 Rating (152 Votes )

There are 3 Steps involved in it

a State Diagram for the Mooretype FSM To detect the sequence 10 in a Mooretyp... View full answer

Get step-by-step solutions from verified subject matter experts

Document Format (2 attachments)

609a6acd6cb06_30598.pdf

180 KBs PDF File

609a6acd6cb06_30598.docx

120 KBs Word File