Question: Can someone please help with this VHDL program? You should try to use only the synthesizable features of VHDL. In particular, only one wait statement

Can someone please help with this VHDL program? You should try to use only the synthesizable features of VHDL. In particular, only one "wait" statement is allowed in a process. The "wait for" statements are not allowed in your implementation, but might be used in your test benches.

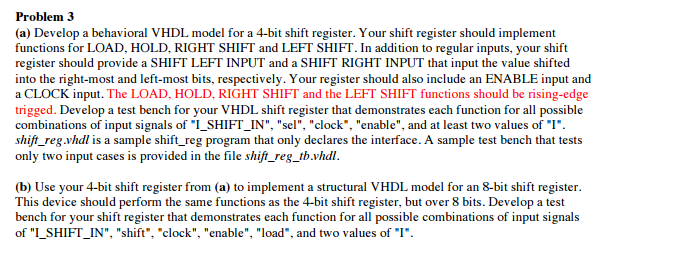

Problem 3 (a) Develop a behavioral VHDL model for a 4-bit shift register. Your shift register should implement functions for LOAD, HOLD, RIGHT SHIFT and LEFT SHIFT.In addition to regular inputs, your shift register should provide a SHIFT LEFT INPUT and a SHIFT RIGHT INPUT that input the value shifted into the right-most and left-most bits, respectively. Your register should also include an ENABLE input and a CLOCK input. The LOAD, HOLD, RIGHT SHIFT and the LEFT SHIFT functions should be rising-edge trigged. Develop a test bench for your VHDL shift register that demonstrates each function for all possible combinations of input signals of "I SHIFT IN "sel", clock enable and at least two values of I shift reg.vhdl is a sample shift reg program that only declares the interface. A sample test bench that tests only two input cases is provided in the file shift reg tb.vhdl (b) Use your 4-bit shift register from (a) to implement a structural VHDL model for an 8-bit shift register This device should perform the same functions as the 4-bit shift register, but over 8 bits. Develop a test bench for your shift register that demonstrates each function for all possible combinations of input signals of "I SHIFT IN" shift clock" enable "load", and two values of I Problem 3 (a) Develop a behavioral VHDL model for a 4-bit shift register. Your shift register should implement functions for LOAD, HOLD, RIGHT SHIFT and LEFT SHIFT.In addition to regular inputs, your shift register should provide a SHIFT LEFT INPUT and a SHIFT RIGHT INPUT that input the value shifted into the right-most and left-most bits, respectively. Your register should also include an ENABLE input and a CLOCK input. The LOAD, HOLD, RIGHT SHIFT and the LEFT SHIFT functions should be rising-edge trigged. Develop a test bench for your VHDL shift register that demonstrates each function for all possible combinations of input signals of "I SHIFT IN "sel", clock enable and at least two values of I shift reg.vhdl is a sample shift reg program that only declares the interface. A sample test bench that tests only two input cases is provided in the file shift reg tb.vhdl (b) Use your 4-bit shift register from (a) to implement a structural VHDL model for an 8-bit shift register This device should perform the same functions as the 4-bit shift register, but over 8 bits. Develop a test bench for your shift register that demonstrates each function for all possible combinations of input signals of "I SHIFT IN" shift clock" enable "load", and two values of

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts