Question: 1 2 . 1 . 5 Design a Verilog model for an 8 - bit Ripple Carry Adder ( RCA ) using a structural design

Design a Verilog model for an bit Ripple

Carry Adder RCA using a structural design

approach. This involves creating a half adder

halfadder.v full adder fulladder.v and

then finally a toplevel adder rcav by

instantiating eight full adder subsystems.

Model the logic operations using gate level

primitives. Give each gate primitive a delay of

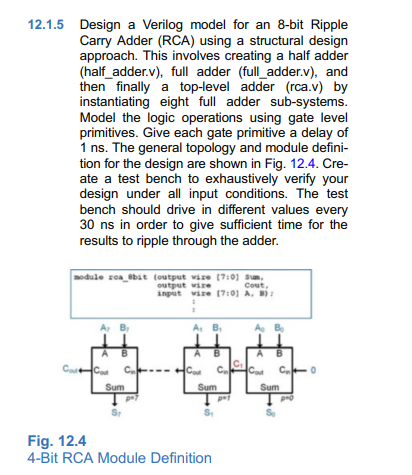

The general topology and module defini

tion for the design are shown in Fig. Cre

ate a test bench to exhaustively verify your

design under all input conditions. The test

bench should drive in different values every

in order to give sufficient time for the

results to ripple through the adder.

Fig.

Bit RCA Module DefinitionDesign a Verilog model for an bit Ripple Carry Adder RCA using a structural design approach. This involves creating a half adder halfadder.v full adder fulladder.v and

then finally a toplevel adder rcav by instantiating eight full adder subsystems. Model the logic operations using gate level primitives. Give each gate primitive a delay of

ns The general topology and module definition for the design are shown in the textbook Fig. page Create a test bench to exhaustively verify your design under all input conditions. The test bench should drive in different values every ns in order to give sufficient time for the results to ripple through the adder.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock