Question: 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. What design principle does the fast integer multiplier demonstrate best:

1.

2.

3.

3.

4.

4.

5.

5.

6.

6.

7.

7.

8.

8.

9.

9.

10.

10.

11.

11.

12.

12.

13.

13.

14.

14.

15.

15.

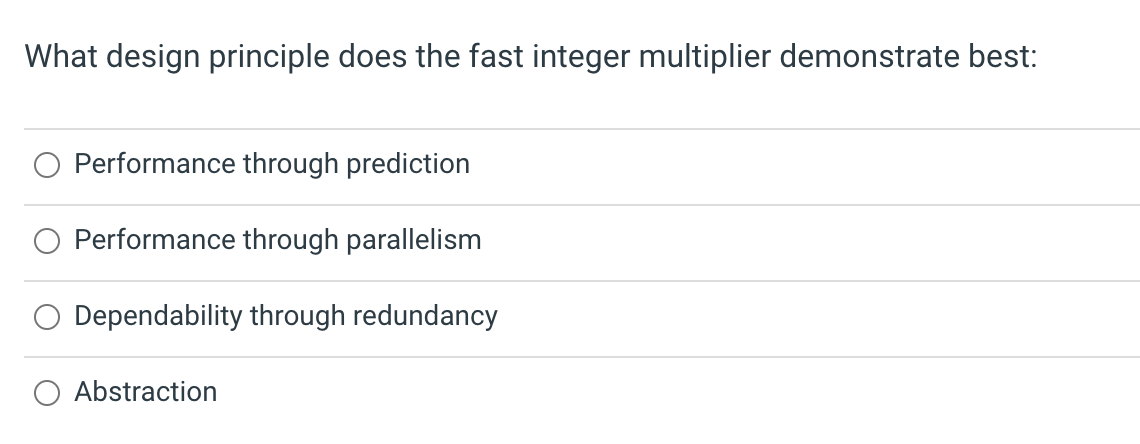

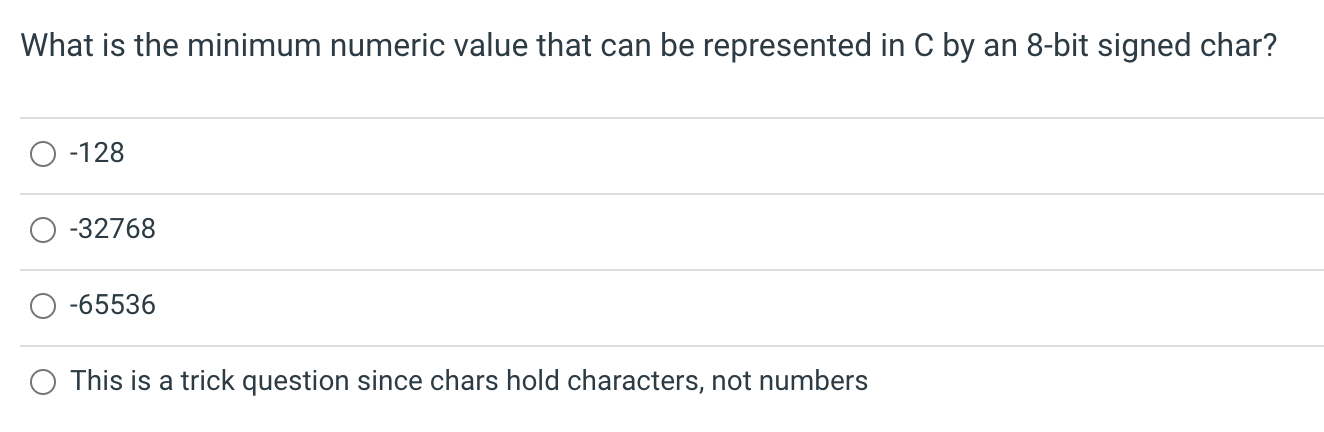

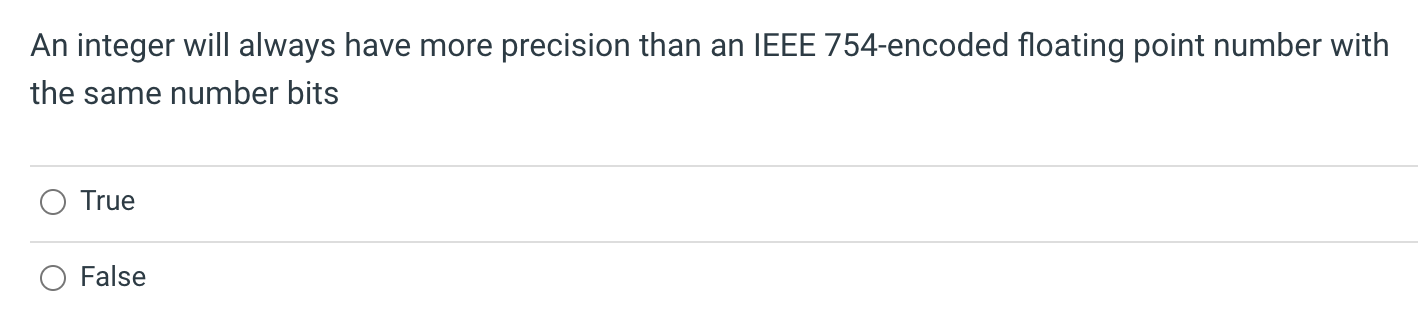

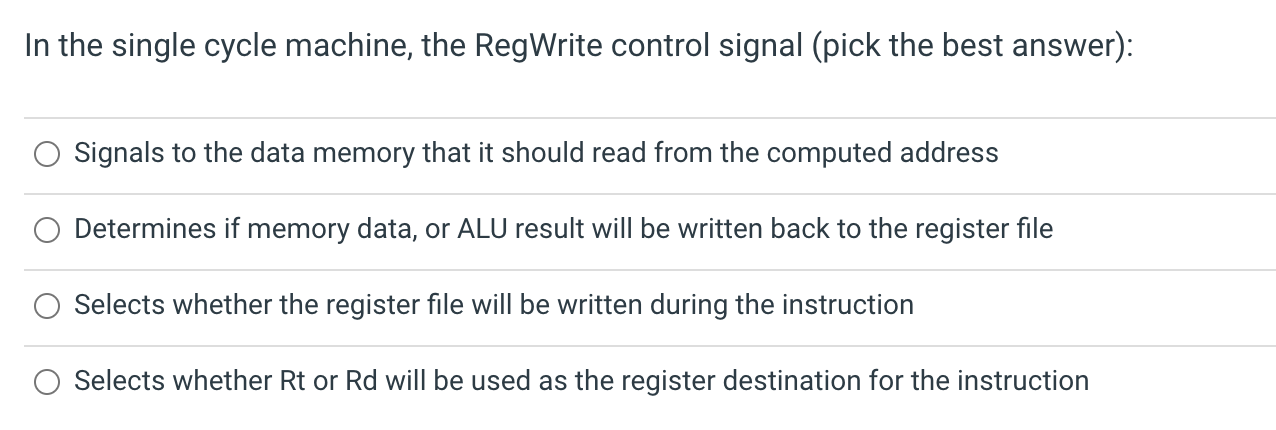

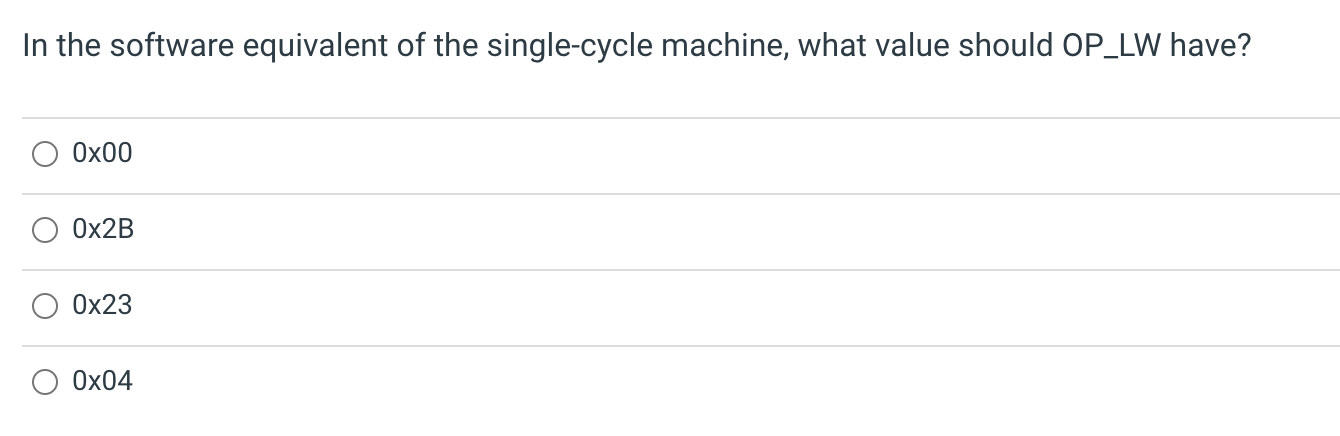

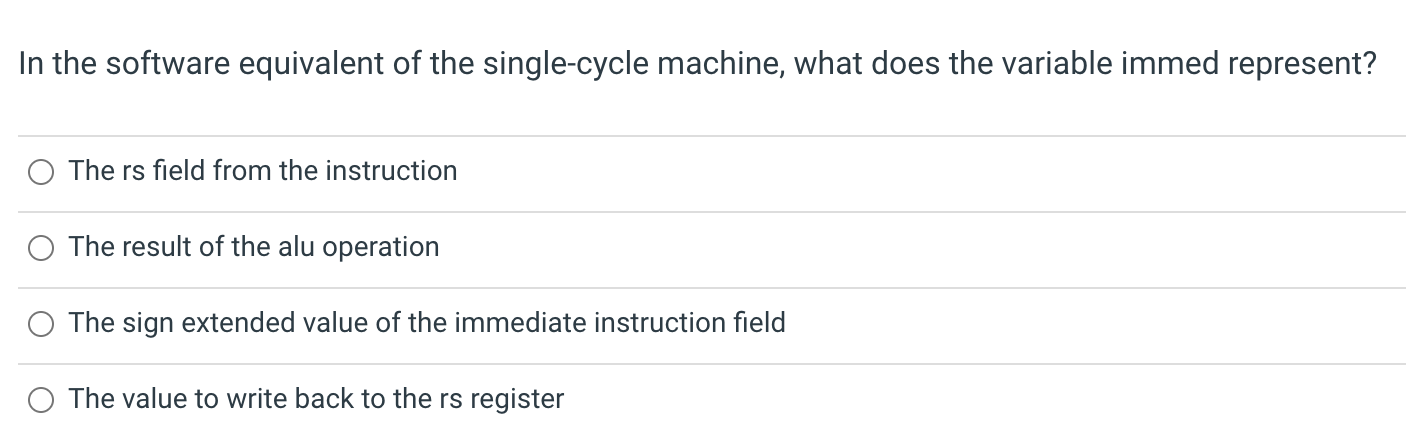

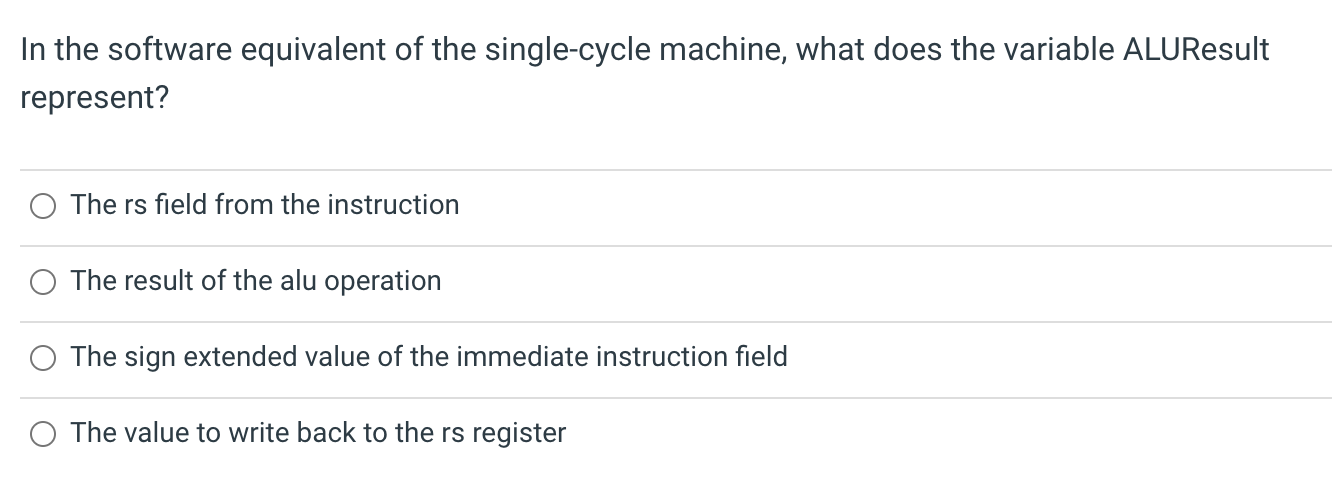

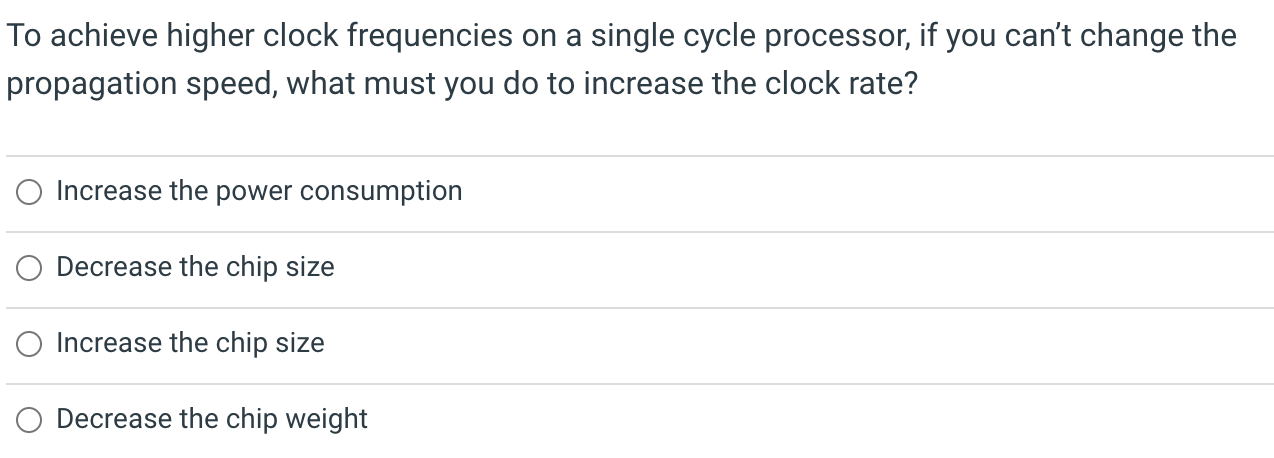

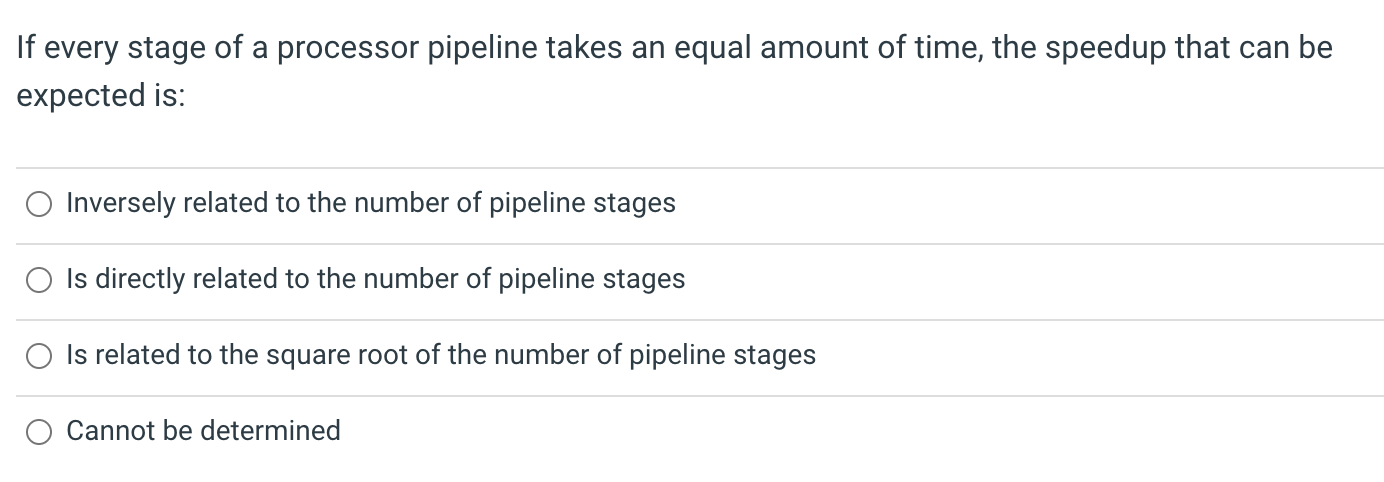

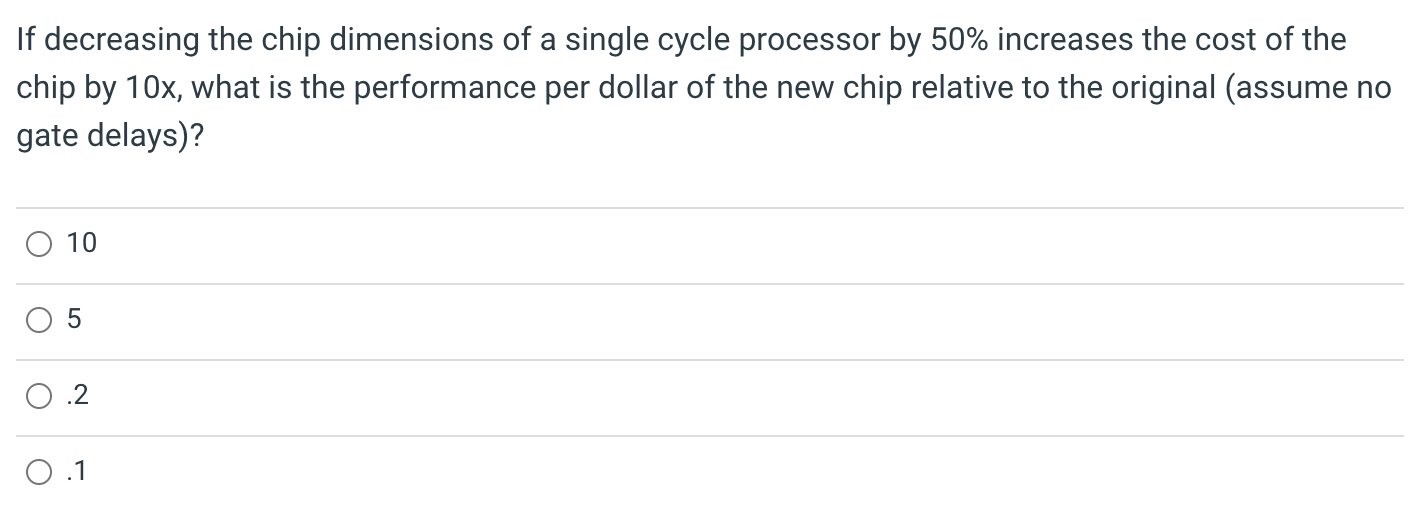

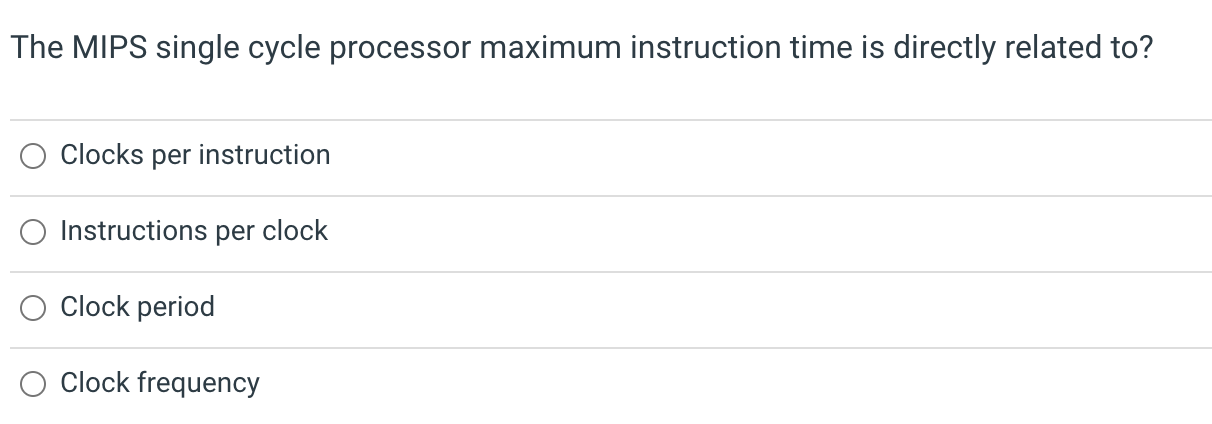

What design principle does the fast integer multiplier demonstrate best: Performance through prediction Performance through parallelism Dependability through redundancy Abstraction What is the minimum numeric value that can be represented in C by an 8-bit signed char? \begin{tabular}{l} 128 \\ \hline32768 \\ \hline65536 \end{tabular} This is a trick question since chars hold characters, not numbers An integer will always have more precision than an IEEE 754-encoded floating point number with the same number bits True False In the single cycle machine, the RegWrite control signal (pick the best answer): Signals to the data memory that it should read from the computed address Determines if memory data, or ALU result will be written back to the register file Selects whether the register file will be written during the instruction Selects whether Rt or Rd will be used as the register destination for the instruction In the single cycle machine, the ALU control output is determined by: The opcode for R-type instructions, otherwise the opcode and function The opcode and function for R-type instructions, otherwise just the opcode The opcode only The function field only Which is not true of the register file: It maintains its contents after turning off the processor power. It holds data to be operated on by instructions Its contents are accessed using the Rs, Rt, and Rd fields from the decoded instruction. Loads from memory are stored into it From the text, which of the following is not a functional block in the single-cycle processor? Instruction Memory Arithmetic Logic Unity (ALU) Data Cache Registers In the software equivalent of the single-cycle machine, what does the variable next_pc represent? The rs field from the instruction The result of the alu operation The sign extended value of the immediate instruction field The value that the program counter should have at the beginning of the next clock cycle. In the software equivalent of the single-cycle machine, what value should OP_LW have? 000 02B 023 004 In the software equivalent of the single-cycle machine, what does the variable immed represent? The rs field from the instruction The result of the alu operation The sign extended value of the immediate instruction field The value to write back to the rs register In the software equivalent of the single-cycle machine, what does the variable ALUResult represent? The rs field from the instruction The result of the alu operation The sign extended value of the immediate instruction field The value to write back to the rs register To achieve higher clock frequencies on a single cycle processor, if you can't change the propagation speed, what must you do to increase the clock rate? Increase the power consumption Decrease the chip size Increase the chip size Decrease the chip weight If every stage of a processor pipeline takes an equal amount of time, the speedup that can be expected is: Inversely related to the number of pipeline stages Is directly related to the number of pipeline stages Is related to the square root of the number of pipeline stages Cannot be determined If decreasing the chip dimensions of a single cycle processor by 50% increases the cost of the chip by 10x, what is the performance per dollar of the new chip relative to the original (assume no gate delays)? 10 5 .2 .1 The MIPS single cycle processor maximum instruction time is directly related to? Clocks per instruction Instructions per clock Clock period Clock frequency

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts