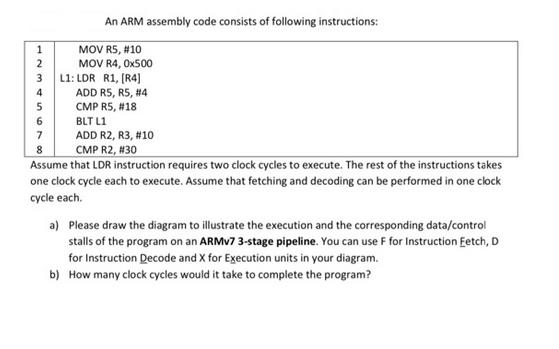

Question: 1 2 3 4 5 6 7 8 An ARM assembly code consists of following instructions: MOV R5, #10 MOV R4,0x500 L1: LDR R1,

1 2 3 4 5 6 7 8 An ARM assembly code consists of following instructions: MOV R5, #10 MOV R4,0x500 L1: LDR R1, [R4] ADD R5, R5, #4 CMP R5, #18 BLT L1 ADD R2, R3, #10 CMP R2, #30 Assume that LDR instruction requires two clock cycles to execute. The rest of the instructions takes one clock cycle each to execute. Assume that fetching and decoding can be performed in one clock cycle each. a) Please draw the diagram to illustrate the execution and the corresponding data/control stalls of the program on an ARMv7 3-stage pipeline. You can use F for Instruction Eetch, D for Instruction Decode and X for Execution units in your diagram. b) How many clock cycles would it take to complete the program?

Step by Step Solution

3.38 Rating (154 Votes )

There are 3 Steps involved in it

a Heres the diagram illustrating the execution and corresponding ... View full answer

Get step-by-step solutions from verified subject matter experts