Question: 1. 2. 3. 4. 5. 6. 7. Which elements are involved in the IF stage of the MIPS pipeline? Program counter, Instruction Memory, and program

1.

2.

2.

3.

3.

4.

4.

5.

5.

6.

6.

7.

7.

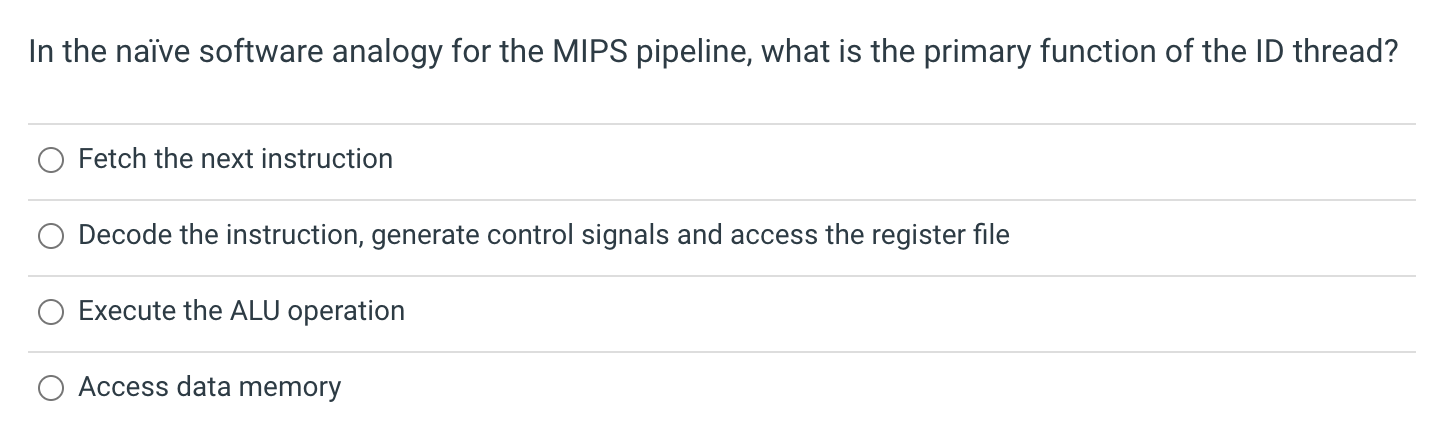

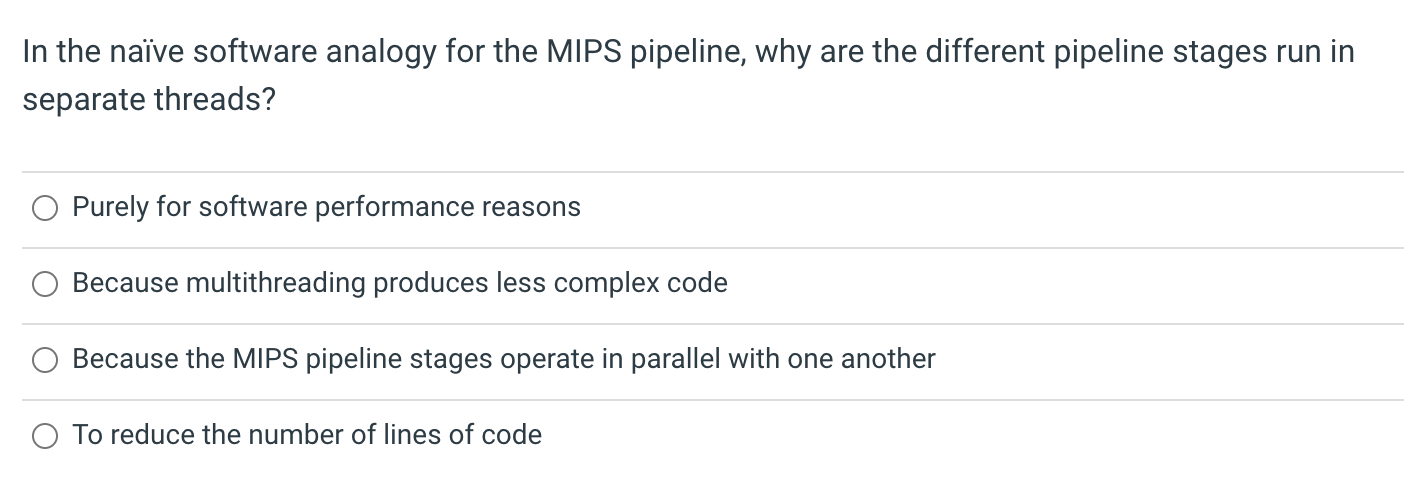

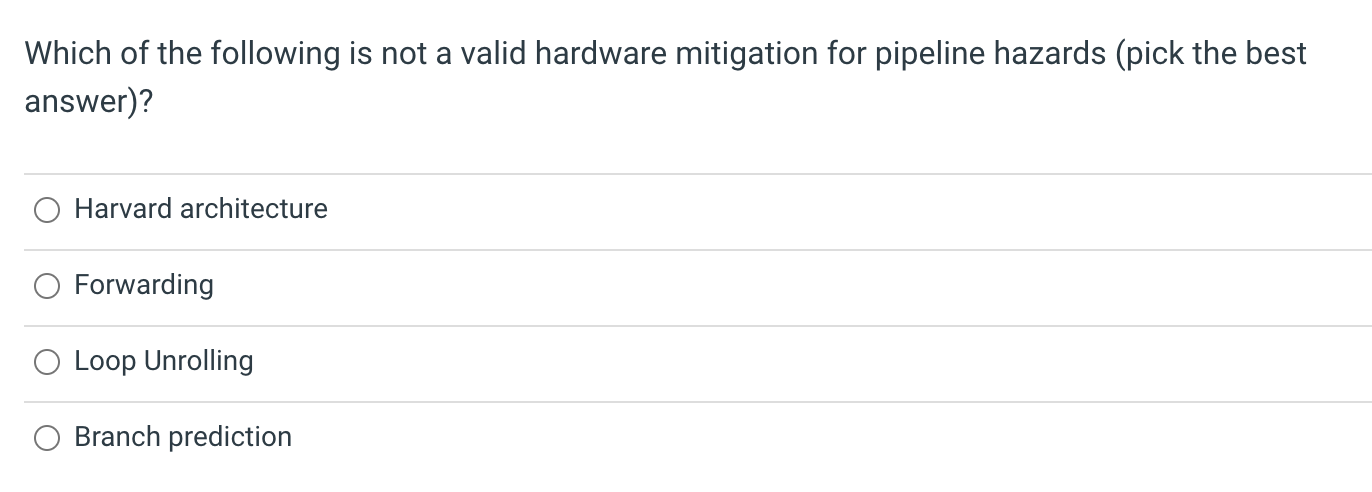

Which elements are involved in the IF stage of the MIPS pipeline? Program counter, Instruction Memory, and program counter adder Register file, control logic, and sign extension ALU and branch adder ata memory The hardware mitigation for data hazards in the MIPS pipeline architecture is to Branch prediction Separate instruction and data memory Reorder instructions Forwarding Which elements are involved in the ID stage of the MIPS pipeline? Program counter, Instruction Memory, and program counter adder Register file, control logic, and sign extension ALU and branch adder Data memory Pipelined processors get their additional performance by executing multiple instructions in parallel True False In the nave software analogy for the MIPS pipeline, what is the primary function of the ID thread? Fetch the next instruction Decode the instruction, generate control signals and access the register file Execute the ALU operation Access data memory In the nave software analogy for the MIPS pipeline, why are the different pipeline stages run in separate threads? Purely for software performance reasons Because multithreading produces less complex code Because the MIPS pipeline stages operate in parallel with one another To reduce the number of lines of code Which of the following is not a valid hardware mitigation for pipeline hazards (pick the best answer)? Harvard architecture Forwarding Loop Unrolling Branch prediction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts