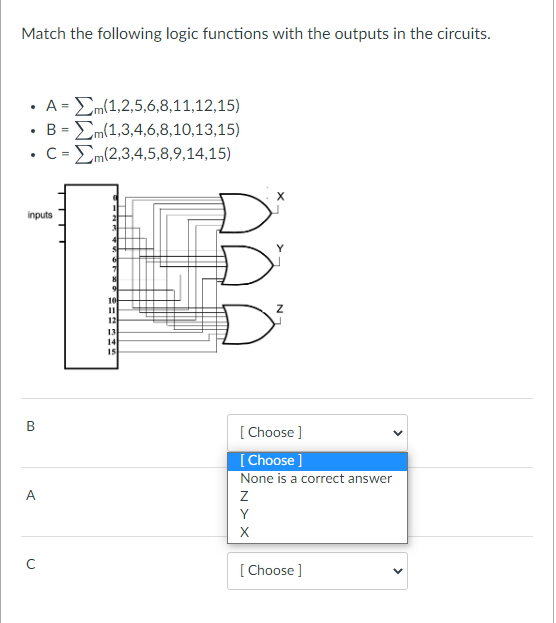

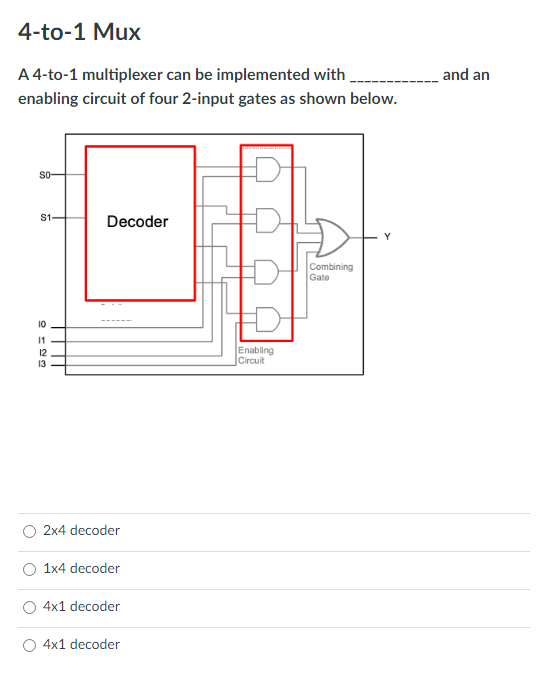

Question: 1. 2. 3. 4. 5. Match the following logic functions with the outputs in the circuits. - A=m(1,2,5,6,8,11,12,15) - B=m(1,3,4,6,8,10,13,15) - C=m(2,3,4,5,8,9,14,15) A 4-to-1 multiplexer

1.

2.

3.

4.

5.

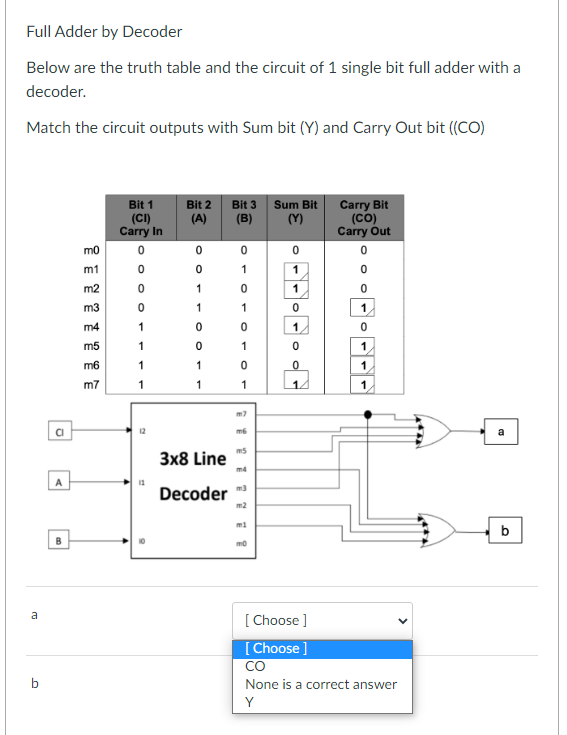

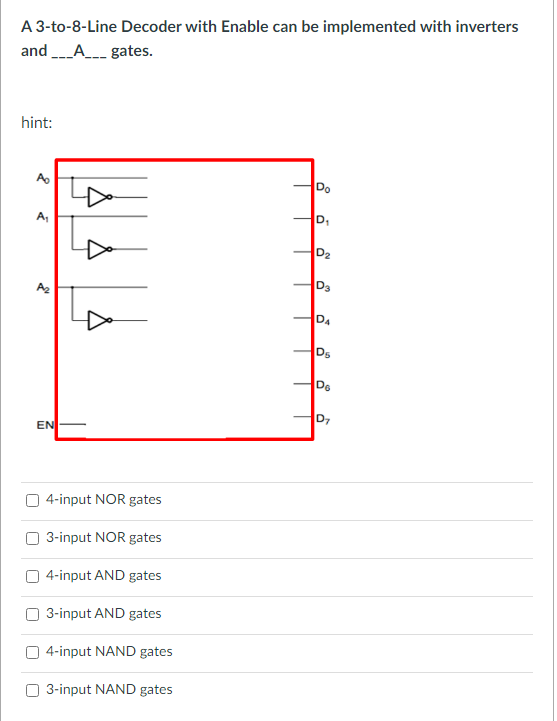

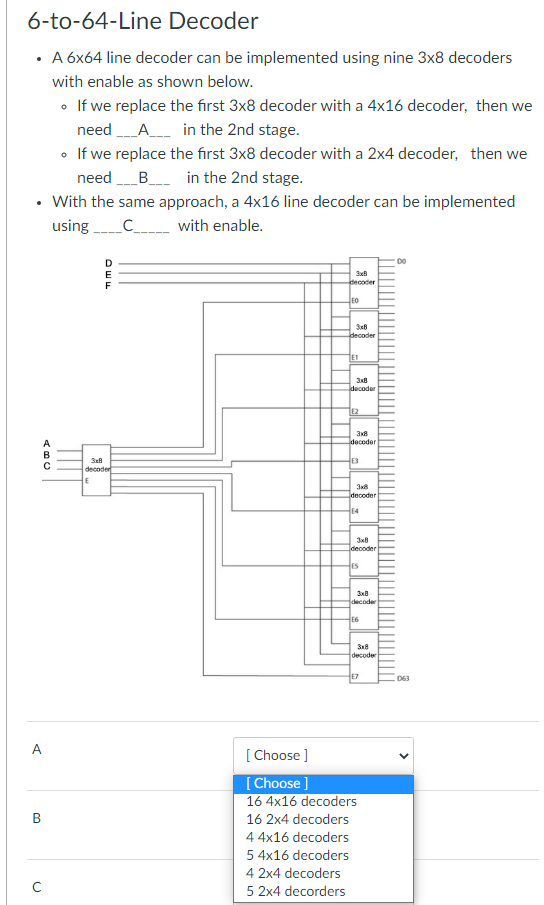

Match the following logic functions with the outputs in the circuits. - A=m(1,2,5,6,8,11,12,15) - B=m(1,3,4,6,8,10,13,15) - C=m(2,3,4,5,8,9,14,15) A 4-to-1 multiplexer can be implemented with and an enabling circuit of four 2-input gates as shown below. 24 decoder 14 decoder 41 decoder 41 decoder Full Adder by Decoder Below are the truth table and the circuit of 1 single bit full adder with a decoder. Match the circuit outputs with Sum bit (Y) and Carry Out bit ((CO) A 3-to-8-Line Decoder with Enable can be implemented with inverters and ___ \( A_{\text {-_- gates. }} \). hint: 4-input NOR gates 3-input NOR gates 4-input AND gates 3-input AND gates 4-input NAND gates 3-input NAND gates 6-to-64-Line Decoder - A 664 line decoder can be implemented using nine 38 decoders with enable as shown below. - If we replace the first 38 decoder with a 416 decoder, then we need ___ Ain the 2 nd stage. - If we replace the first 38 decoder with a 24 decoder, then we need ___ B in the 2 nd stage. - With the same approach, a 416 line decoder can be implemented using Cwith enable

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts