Question: 1) 2) 3) Write a VHDL code to implement this 1-bit ALU slide Test all functions of this 1-bit ALU slice using their Truth tables

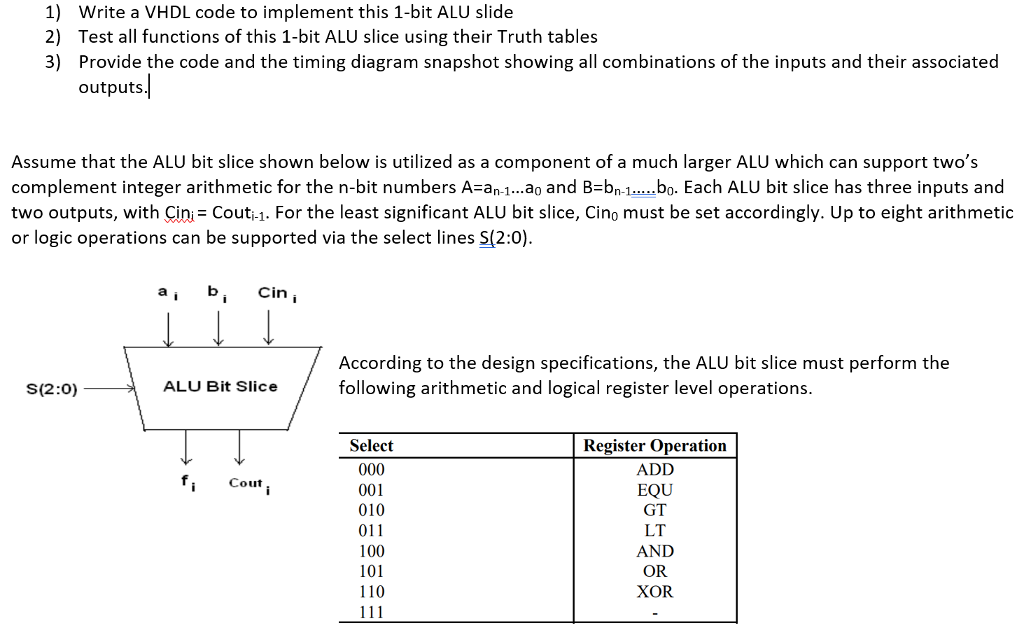

1) 2) 3) Write a VHDL code to implement this 1-bit ALU slide Test all functions of this 1-bit ALU slice using their Truth tables Provide the code and the timing diagram snapshot showing all combinations of the inputs and their associated outputs Assume that the ALU bit slice shown below is utilized as a component of a much larger ALU which can support two's complement integer arithmetic for the n-bit numbers A-an-1...ao and B-brn-1. .bo. Each ALU bit slice has three inputs and two outputs, with Cini Cout-1. For the least significant ALU bit slice, Cino must be set accordingly. Up to eight arithmetic or logic operations can be supported via the select lines S(2:0) i Cin According to the design specifications, the ALU bit slice must perform the following arithmetic and logical register level operations S(2:0) ALU Bit Slice Select Register Operation ADD EQU GT LT AND OR XOR Cout 001 011 100 101 110 1) 2) 3) Write a VHDL code to implement this 1-bit ALU slide Test all functions of this 1-bit ALU slice using their Truth tables Provide the code and the timing diagram snapshot showing all combinations of the inputs and their associated outputs Assume that the ALU bit slice shown below is utilized as a component of a much larger ALU which can support two's complement integer arithmetic for the n-bit numbers A-an-1...ao and B-brn-1. .bo. Each ALU bit slice has three inputs and two outputs, with Cini Cout-1. For the least significant ALU bit slice, Cino must be set accordingly. Up to eight arithmetic or logic operations can be supported via the select lines S(2:0) i Cin According to the design specifications, the ALU bit slice must perform the following arithmetic and logical register level operations S(2:0) ALU Bit Slice Select Register Operation ADD EQU GT LT AND OR XOR Cout 001 011 100 101 110

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts