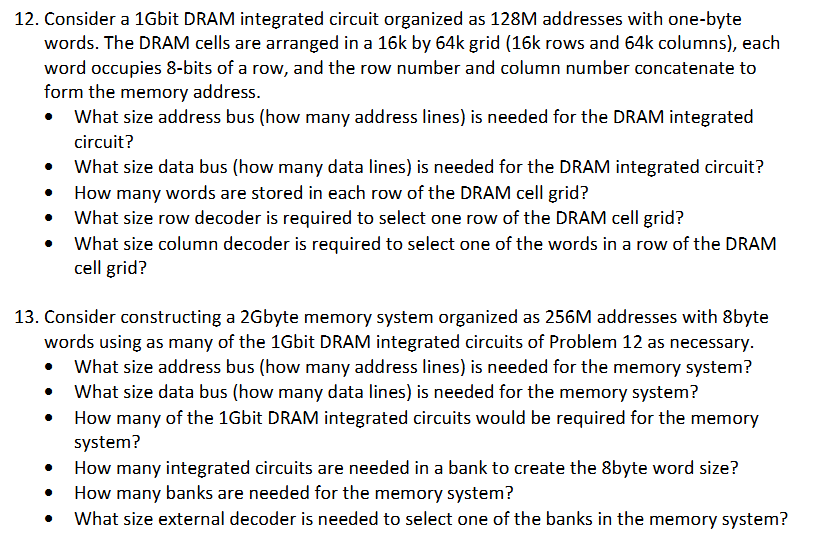

Question: 1 2 . Consider a 1 Gbit DRAM integrated circuit organized as 1 2 8 M addresses with one - byte words. The DRAM cells

Consider a Gbit DRAM integrated circuit organized as M addresses with onebyte words. The DRAM cells are arranged in a k by k grid k rows and k columns each word occupies bits of a row, and the row number and column number concatenate to form the memory address.

What size address bus how many address lines is needed for the DRAM integrated circuit?

What size data bus how many data lines is needed for the DRAM integrated circuit?

How many words are stored in each row of the DRAM cell grid?

What size row decoder is required to select one row of the DRAM cell grid?

What size column decoder is required to select one of the words in a row of the DRAM cell grid?

Consider constructing a Gbyte memory system organized as M addresses with byte words using as many of the Gbit DRAM integrated circuits of Problem as necessary.

What size address bus how many address lines is needed for the memory system?

What size data bus how many data lines is needed for the memory system?

How many of the Gbit DRAM integrated circuits would be required for the memory system?

How many integrated circuits are needed in a bank to create the byte word size?

How many banks are needed for the memory system?

What size external decoder is needed to select one of the banks in the memory system?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock