Question: 1. 2. The pipelined MIPS datapath executes the following program. add $51, $s2, $to sub $to, $t1, $t2 lw $t3, 15($51) sw $t5, 72($t0) or

1.

2.

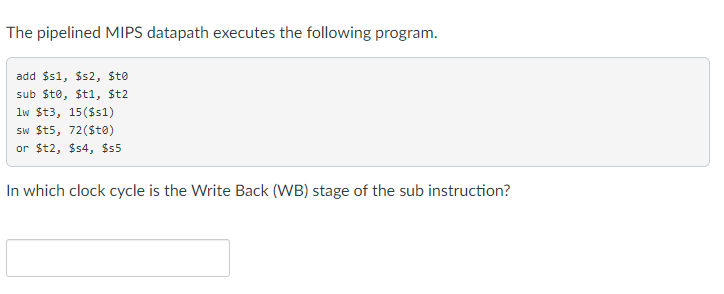

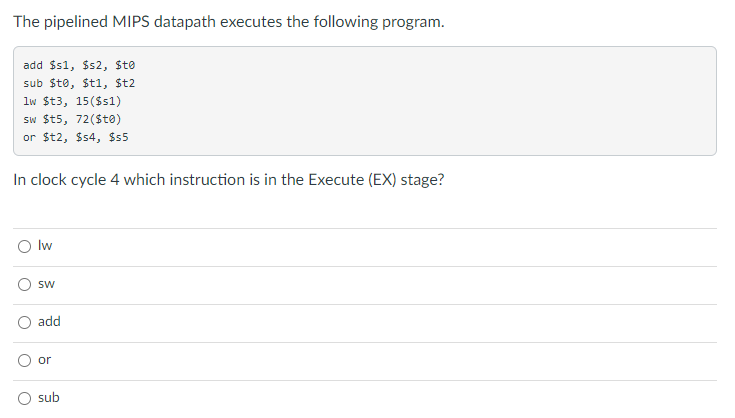

The pipelined MIPS datapath executes the following program. add $51, $s2, $to sub $to, $t1, $t2 lw $t3, 15($51) sw $t5, 72($t0) or $t2, $54, $55 In which clock cycle is the Write Back (WB) stage of the sub instruction? The pipelined MIPS datapath executes the following program. add $s1, $s2, $to sub $to, $t1, $t2 lw $t3, 15($51) sw $t5, 72($to) or $t2, $s4, $55 In clock cycle 4 which instruction is in the Execute (EX) stage? lw O SW O add or O sub

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts