Question: 1. (30 pts) The basic pipeline for DLX has five stages: IF, ID, EX, MEM, and WB. Assuming all memory accesses take 1 clock cycle

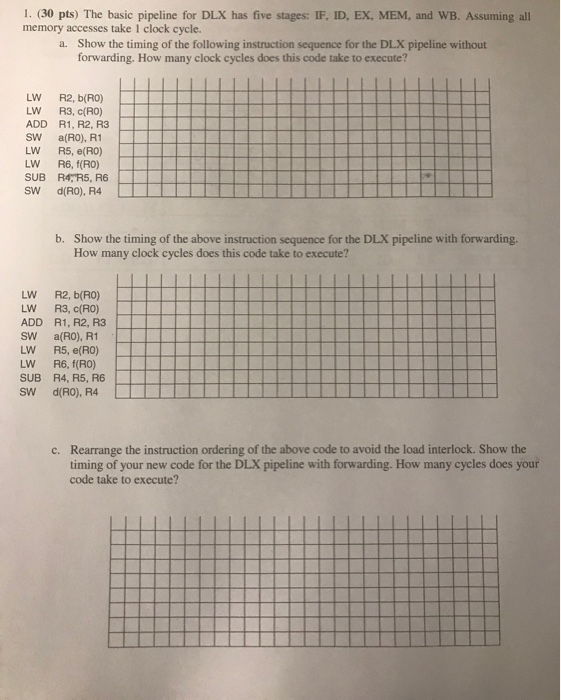

1. (30 pts) The basic pipeline for DLX has five stages: IF, ID, EX, MEM, and WB. Assuming all memory accesses take 1 clock cycle a. Show the timing of the following instruction sequence for the DLX pipeline without forwarding. How many clock cycles does this code take to execute? LW R2, b(RO) LW R3, c(RO) ADD R1, R2, R3 SW a(RO), R1 LW R5, e(RO) LW R6, f(RO) SUB R4:R5, R6 SW d(RO), R4 b. Show the timing of the above instruction sequence for the DLX pipeline with forwarding. How many clock cycles does this code take to execute? LW R2, b(RO) LW R3, c(RO) ADD R1, R2, R3 sw a(RO), R1 LW R5, e(RO) LW R6, f(RO) SUB R4, R5, R6 SW d(RO), R4 Rearrange the instruction ordering of the above code to avoid the load interlock. Show the timing of your new code for the DLX pipeline with forwarding. How many cycles does your code take to execute? c

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts