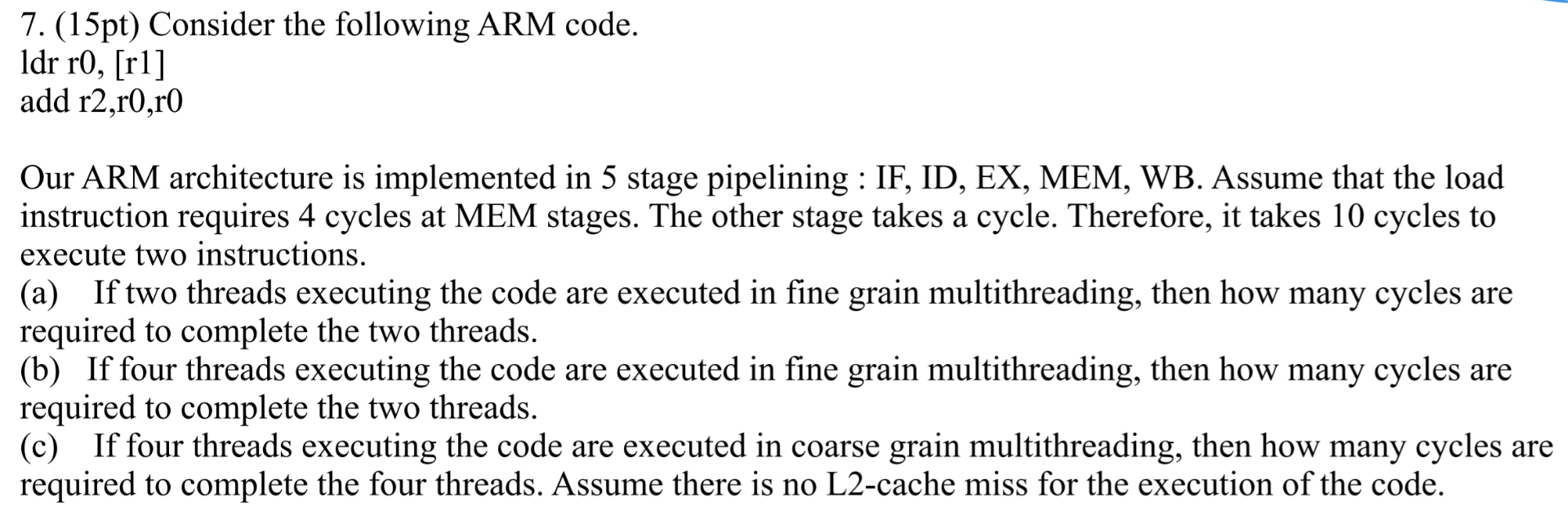

Question: ( 1 5 pt ) Consider the following ARM code. ldr r 0 , [ r 1 ] add r 2 , r 0 ,

pt Consider the following ARM code.

ldr rr

add rrr

Our ARM architecture is implemented in stage pipelining: IF ID EX MEM, WB Assume that the load instruction requires cycles at MEM stages. The other stage takes a cycle. Therefore, it takes cycles to execute two instructions.

a If two threads executing the code are executed in fine grain multithreading, then how many cycles are required to complete the two threads.

b If four threads executing the code are executed in fine grain multithreading, then how many cycles are required to complete the two threads.

c If four threads executing the code are executed in coarse grain multithreading, then how many cycles are required to complete the four threads. Assume there is no Lcache miss for the execution of the code.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock