Question: 1. Below is the datapath for a sequential system which computes the arithmetic mean of upto fifteen 8-bit binary integers. The 8-bit integers are inputs

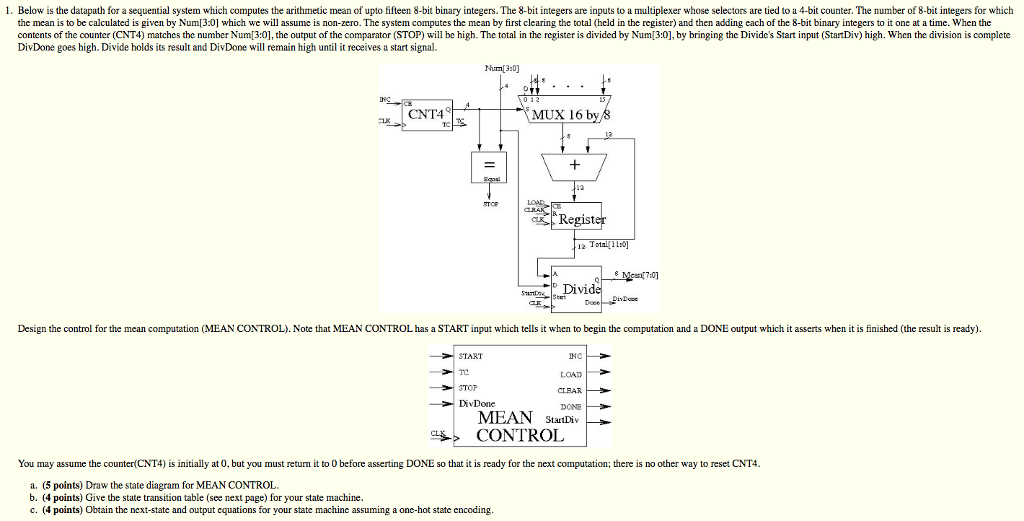

1. Below is the datapath for a sequential system which computes the arithmetic mean of upto fifteen 8-bit binary integers. The 8-bit integers are inputs to a multiplexer whose selectors are tied to a 4-bit counter. The number of 8-bit integers for which the mean is to be calculated is given by Num 3:0] which we will assume is non-zero. The system computes the mean by first clearing the total (held in the register) and then adding each of the 8-bit binary integers to it one at a time. When the contents of the counter (CNT4) matches the number Num[3:0], the output of the comparator (STOP) will be high. The total in the register is divided by Num[3:0], by bringing the Divide's Start input (StartDiv) high. When the division is complete DivDone goes high. Divide holds its result and DivDone will remain high until it receives a start signal. Nurn 3:0) CNT4 MUX 16 Regist 12 Total II:o] 7:0] Divid Design the control for the mean computation (MEAN CONTROL). Note that MEAN CONTROL has a START input which tells it when to begin the computation and a DONE output which it asserts when it is finished (the result is ready) START INC LOAD CLEAR DivDone MEAN StatDi CONTROL You may assume the counter(CNT4) is initially at 0, but you must return it to O before asserting DONE so that it is ready for the next computation; there is no other way to reset CNT4 a. (5 points) Draw the state diagram for MEAN CONTROL b. (4 points) Give the state transition table (see next page) for your state machine. c. (4 points) Obtain the next-state and output equations for your state machine assuming a one-hot state encoding 1. Below is the datapath for a sequential system which computes the arithmetic mean of upto fifteen 8-bit binary integers. The 8-bit integers are inputs to a multiplexer whose selectors are tied to a 4-bit counter. The number of 8-bit integers for which the mean is to be calculated is given by Num 3:0] which we will assume is non-zero. The system computes the mean by first clearing the total (held in the register) and then adding each of the 8-bit binary integers to it one at a time. When the contents of the counter (CNT4) matches the number Num[3:0], the output of the comparator (STOP) will be high. The total in the register is divided by Num[3:0], by bringing the Divide's Start input (StartDiv) high. When the division is complete DivDone goes high. Divide holds its result and DivDone will remain high until it receives a start signal. Nurn 3:0) CNT4 MUX 16 Regist 12 Total II:o] 7:0] Divid Design the control for the mean computation (MEAN CONTROL). Note that MEAN CONTROL has a START input which tells it when to begin the computation and a DONE output which it asserts when it is finished (the result is ready) START INC LOAD CLEAR DivDone MEAN StatDi CONTROL You may assume the counter(CNT4) is initially at 0, but you must return it to O before asserting DONE so that it is ready for the next computation; there is no other way to reset CNT4 a. (5 points) Draw the state diagram for MEAN CONTROL b. (4 points) Give the state transition table (see next page) for your state machine. c. (4 points) Obtain the next-state and output equations for your state machine assuming a one-hot state encoding

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts