Question: 1. Design and implement a modified Verilog module to have it increment through one second intervals with improved accuracy. Do this by completing the module

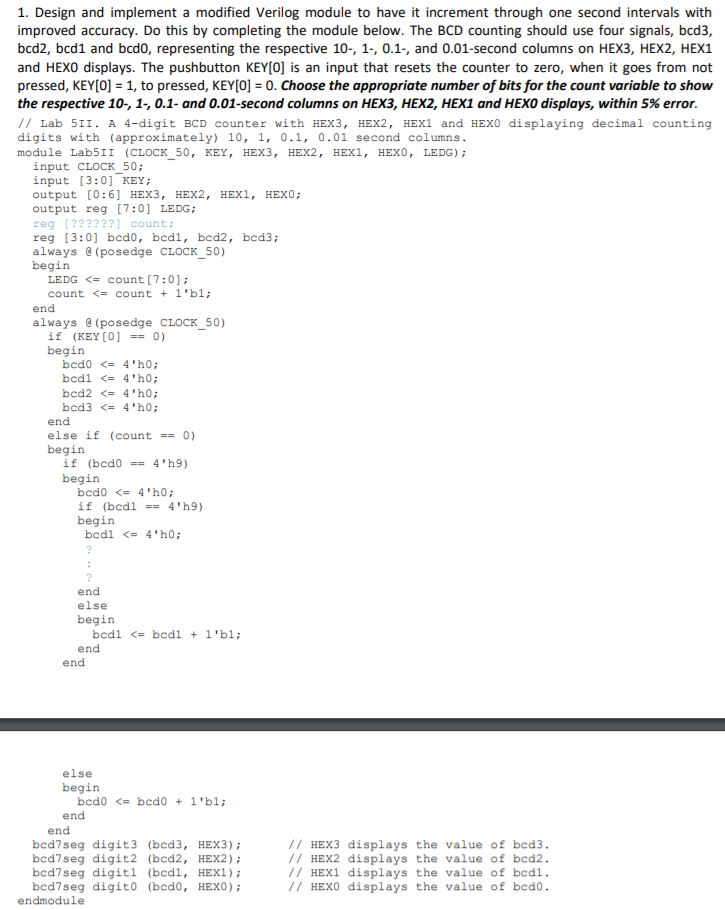

1. Design and implement a modified Verilog module to have it increment through one second intervals with improved accuracy. Do this by completing the module below. The BCD counting should use four signals, bcd3, bcd2, bcd1 and bcdo, representing the respective 10-, 1-, 0.1, and 0.01-second columns on HEX3, HEX2, HEX1 and HEXO displays. The pushbutton KEY[0] is an input that resets the counter to zero, when it goes from not pressed, KEY[0] = 1, to pressed, KEY[O-0. Choose the appropriate number of bits for the count variable to show the respective 10-, 1-, 0.1-and 0.01-second columns on HEX3, HEX2, HEX1 and HEX0 displays, within 5% error // Lab 5II. A 4-digit BCD counter with HEX3,HEX2, HEX1 and HEX0 displaying decimal counting digits with (approximately) 10, 1, 0.1, 0.01 second columns module LabS 11 (CLOCK 50, KEY, HEX3, HEX2, HEX 1, HEXO, LE DG); input cLOCK 50 input [3:0] KEY output [0:6 HEX3, HEX2, HEX, HEXO; output reg [7:0 LEDG reg [2?????1 count reg [3:0] bcd0, bedl, bed2, bed3; always (posedge CLOCK50) begin LEDG count [7:0; count

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts