Question: 1. If the processor has 32 address lines in its address bus; i.e. 32-bit address range, what is its address space or range; i.e. what

1.

If the processor has 32 address lines in its address bus; i.e. 32-bit address range, what is its address space or range; i.e. what is the smallest and largest address that can be represented?

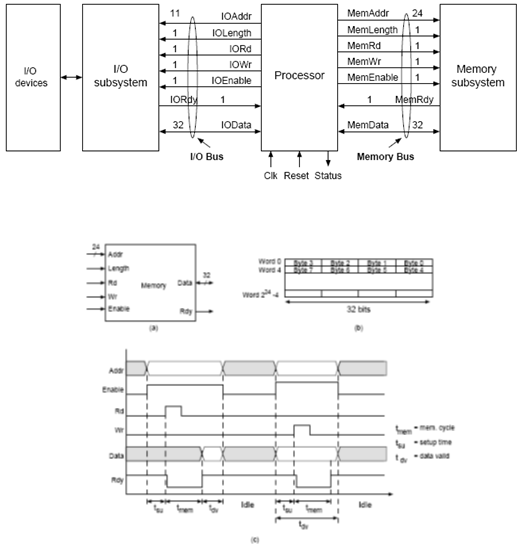

Given the following diagram of a simple processor and memory controller, along with the timing diagram illustrating both a memory read and write operation; describe steps taken by the processor and the responses of the memory controller for each of these operations.

2.

Give the Java statement that produced the following NASM assembly code and explain: section .data K db 3 N db 5 M db 0 .text MOV eax, [K] MOV ecx, [N] ADD eax, ecx ADD eax, 16 SUB eax, eax MOV [M], eax

3.

Compile this assembly code that uses arrays. (Tutorialspoint, n.d.) section .text global _start ;must be declared for linker (ld) _start: mov eax,3 ; Number bytes to be summed mov ebx,0 ; ebx will store the sum mov ecx, x ; ecx will point to the current element to be summed top: add ebx, [ecx] add ecx, 1 ; Move pointer to next element dec eax ; Decrement counter jnz top ; If counter not 0, then loop again done: add ebx, '0' ; INSTRUCTORS QUESTION: Why are we doing this? mov [sum], ebx ; Done, store result in "sum" display: mov edx, 1 ; Message length mov ecx, sum ; Message to write mov ebx, 1 ; File descriptor (stdout) mov eax, 4 ; System call number (sys_write) int 0x80 ; Call Linux kernel mov eax, 1 ; System call number (sys_exit) int 0x80 ; Call Linux kernel section .data global x x: db 2 db 4 db 3 sum: db 0 Use https://www.tutorialspoint.com/compile_assembly_online.php to compile and execute assembly code. Change the program to display an ASCII F as a sum of the array.

11 MemAddr 24 IOAddr Memlength IOLength MemRd IORD MemWr IOWr I/O Memory subsystem VO devices Processor MemEnable IOEnable subsystem IORDY MemRdy 32 32 IOData MemData VO Bus Memory Bus CIk Reset Status word0 Lengh Memory Wors wr 32 bits Ray Enabie men. cycle Data Roy Ide Idie 11 MemAddr 24 IOAddr Memlength IOLength MemRd IORD MemWr IOWr I/O Memory subsystem VO devices Processor MemEnable IOEnable subsystem IORDY MemRdy 32 32 IOData MemData VO Bus Memory Bus CIk Reset Status word0 Lengh Memory Wors wr 32 bits Ray Enabie men. cycle Data Roy Ide Idie

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts