Question: 1. Pipelining Cycle Time Assuming the following worst-case latencies for components, what is the cycle time for the pipelined processor in Figure 4.51 on page

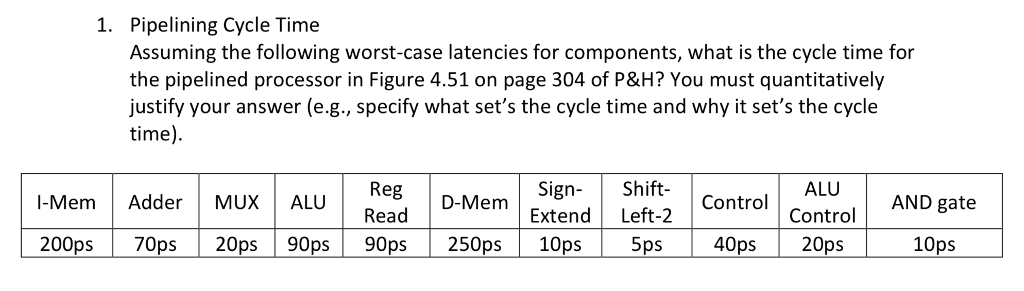

1. Pipelining Cycle Time Assuming the following worst-case latencies for components, what is the cycle time for the pipelined processor in Figure 4.51 on page 304 of P&H? You must quantitatively justify your answer (e.g., specify what sets the cycle time and why it sets the cycle time).

Pipelining Cycle Time Assuming the following worst-case latencies for components, what is the cycle time for the pipelined processor in Figure 4.51 on page 304 of P&H? You must quantitatively justify your answer (e.g., specify what set's the cycle time and why it set's the cycle time). 1. ALU I-Mem Adder MUX ALU ALU Reg AND gate Read DMem Sign-Shift- Extend Left-2 Control 200ps70ps 20ps 90pS 90ps250ps10ps 5ps 40ps 20ps 10ps

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts