Question: 1. Tomasulo A CPU with a Tomasulo engine has two integer units (each capable of doing loads and stores), one floating point unit capable of

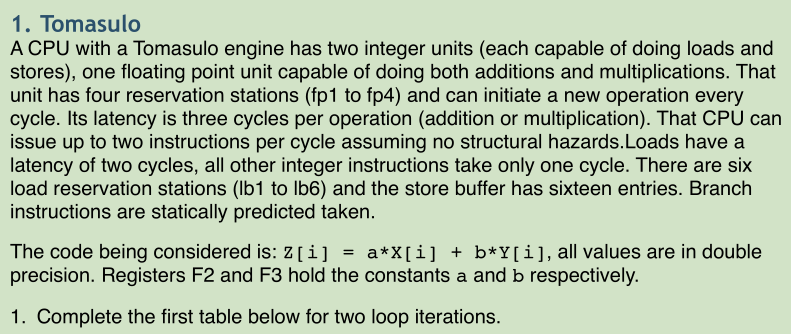

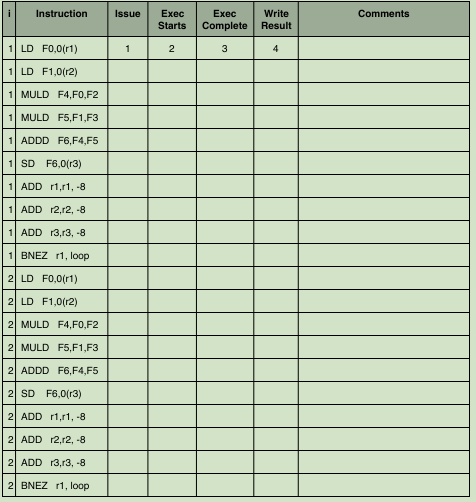

1. Tomasulo A CPU with a Tomasulo engine has two integer units (each capable of doing loads and stores), one floating point unit capable of doing both additions and multiplications. That unit has four reservation stations (fp1 to fp4) and can initiate a new operation every cycle. Its latency is three cycles per operation (addition or multiplication). That CPU can issue up to two instructions per cycle assuming no structural hazards.Loads have a latency of two cycles, all other integer instructions take only one cycle. There are six load reservation stations (lb1 to lb6) and the store buffer has sixteen entries. Branch instructions are statically predicted taken. The code being considered is: z[i ] = a*X[i ] + by[i ], all values are in double precision. Registers F2 and F3 hold the constants a and b respectively. 1. Complete the first table below for two loop iterations. 1. Tomasulo A CPU with a Tomasulo engine has two integer units (each capable of doing loads and stores), one floating point unit capable of doing both additions and multiplications. That unit has four reservation stations (fp1 to fp4) and can initiate a new operation every cycle. Its latency is three cycles per operation (addition or multiplication). That CPU can issue up to two instructions per cycle assuming no structural hazards.Loads have a latency of two cycles, all other integer instructions take only one cycle. There are six load reservation stations (lb1 to lb6) and the store buffer has sixteen entries. Branch instructions are statically predicted taken. The code being considered is: z[i ] = a*X[i ] + by[i ], all values are in double precision. Registers F2 and F3 hold the constants a and b respectively. 1. Complete the first table below for two loop iterations

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts