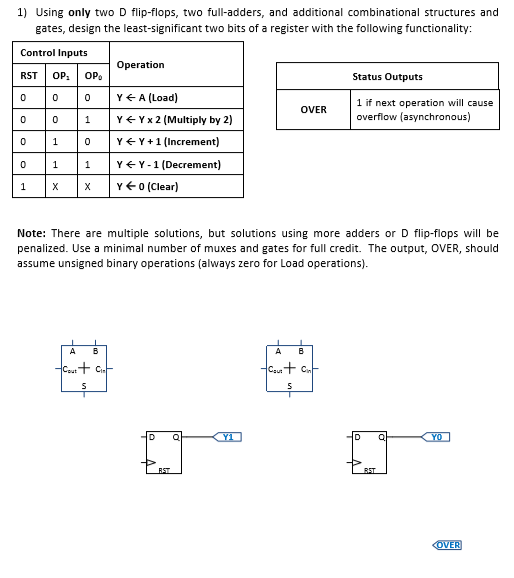

Question: 1) Using only two D flip-flops, two full-adders, and additional combinational structures and gates, design the least-significant two bits of a register with the following

1) Using only two D flip-flops, two full-adders, and additional combinational structures and gates, design the least-significant two bits of a register with the following functionality: Control Inputs Operation Status Outputs | 0 | 0 | 1 | 1 | X | 0 | 1 | 0 | 1 | X | YA (Load) | Y Y x 2 (Multiply by 2) | Y Y + 1 (increment) | Y -Y-1 (Decrement) | Y 0 (Clear) 0 1 if next operation will cause overflow (asynchronous) OVER 0 0 Note: There are multiple solutions, but solutions using more adders or D flip-flops will be penalized. Use a minimal number of muxes and gates for full credit. The output, OVER, should assume unsigned binary operations (always zero for Load operations). A B A B Cin OVER

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts