Question: 1 ) Your work by hand ( state diagram ) 2 ) Verilog ( . v ) file ( s ) of the light sequence

Your work by hand state diagram

Verilog v files of the light sequence andor toplevel if you have one

Verilog v file for testbench of light sequence

xdc file

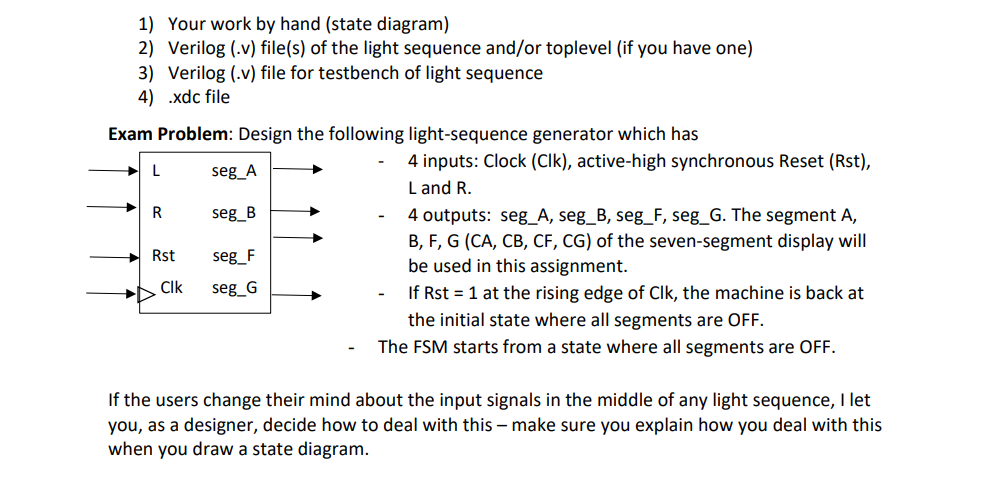

Exam Problem: Design the following lightsequence generator which has

inputs: Clock Clk activehigh synchronous Reset Rst L and R

outputs: segA segB segF segG The segment A B F GC A C B C F C G of the sevensegment display will be used in this assignment.

If Rst at the rising edge of Clk the machine is back at the initial state where all segments are OFF.

The FSM starts from a state where all segments are OFF.

If the users change their mind about the input signals in the middle of any light sequence, I let you, as a designer, decide how to deal with this make sure you explain how you deal with this when you draw a state diagram. The segments A B G F A B G are lit up one at a time. This sequence is repeated as long as L and R

pts Design the circuit draw its state diagram

pts Write a Verilog file to describe your designed circuit

pts Write a testbench to simulate your circuit. Note: your testbench should contain at least case scenarios such as

a L R for at least clock cycles,

b L R for at least clock cycles,

c L R for at least clock cycles,

d the user changes hisher mind about the input signals in the middle of any light sequence. Your waveform for this case should MATCH with your state diagram!

pts Write a toplevel code to connect ClkDiv with your designed circuit.

pts Write a constraint xdc file for the toplevel code and then download your

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock