Question: 1.(6 points-Correctness) Cache Layout: Mario gave Princess Daisy a processor that has a separate D-cache and an l-cache. He is trying to explain how the

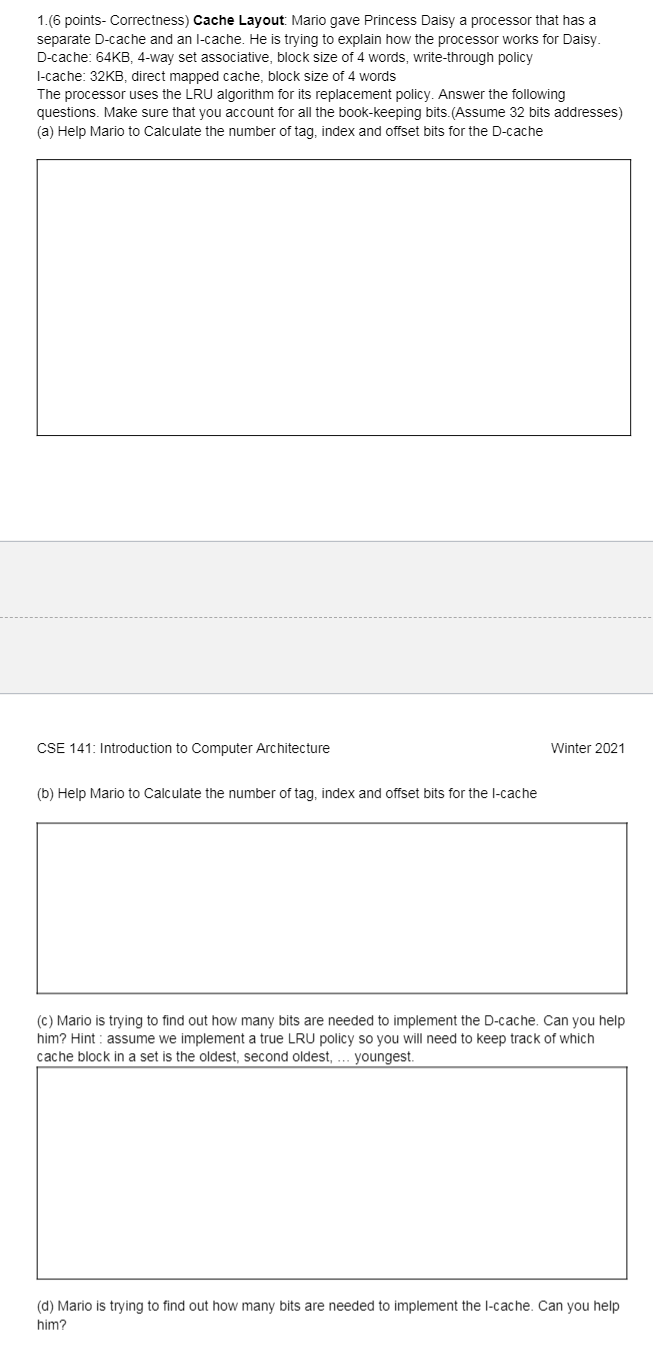

1.(6 points-Correctness) Cache Layout: Mario gave Princess Daisy a processor that has a separate D-cache and an l-cache. He is trying to explain how the processor works for Daisy D-cache: 64KB, 4-way set associative, block size of 4 words, write-through policy l-cache: 32KB, direct mapped cache, block size of 4 words The processor uses the LRU algorithm for its replacement policy. Answer the following questions. Make sure that you account for all the book-keeping bits. Assume 32 bits addresses) (a) Help Mario to Calculate the number of tag, index and offset bits for the D-cache CSE 141: Introduction to Computer Architecture Winter 2021 (b) Help Mario to Calculate the number of tag, index and offset bits for the l-cache (c) Mario is trying to find out how many bits are needed to implement the D-cache. Can you help him? Hint : assume we implement a true LRU policy so you will need to keep track of which cache block in a set is the oldest, second oldest, ... youngest. (d) Mario is trying to find out how many bits are needed to implement the l-cache. Can you help him

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts