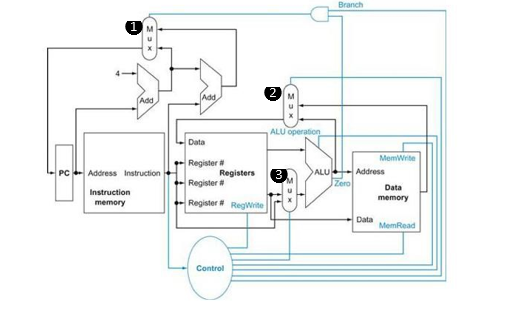

Question: 1.Consider the MIPS load word instruction as implemented on the datapath above: lw R2, 8(R1) // Reg[2] 2.Consider the MIPS store word instruction as implemented

1.Consider the MIPS load word instruction as implemented on the datapath above:

lw R2, 8(R1) // Reg[2]

2.Consider the MIPS store word instruction as implemented on the datapath above

sw R4, -12(R3) // Memory[ Reg[3] + signextended(-12) ]

Circle the correct value 0 or 1 for the control signals (a-d) and circle whether each of the three muxes (e-g) selects its upper input, lower input, or don't care. For the ALU operation (h) circle one of the function names. (The Zero condition signal will be assumed to be 0.)

(a) Branch = 0 1

(b) MemRead = 0 1

(c) MemWrite = 0 1

(d) RegWrite = 0 1

(e) Mux1 (upper left; output to PC) = upper, lower, don't care

(f) Mux2 (upper middle; output to Data port of Regs) = upper, lower, don't care

(g) Mux3 (lower middle; output to bottom leg of ALU) = upper, lower, don't care

(h) ALU operation = and, or, add, subtract, set-on-less-than, nor

Branch Add Add ALU Data Register # Register # Register # RegWrite! PC-Address Instruction Registers ALI Address Instruction memory Data memory Data MemRead Control Branch Add Add ALU Data Register # Register # Register # RegWrite! PC-Address Instruction Registers ALI Address Instruction memory Data memory Data MemRead Control

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts