Question: 2. (21 points) fill in the Blunk (Please write your answer on the line) a) A CPU is running at 2GHz. It tikes 2 cycle

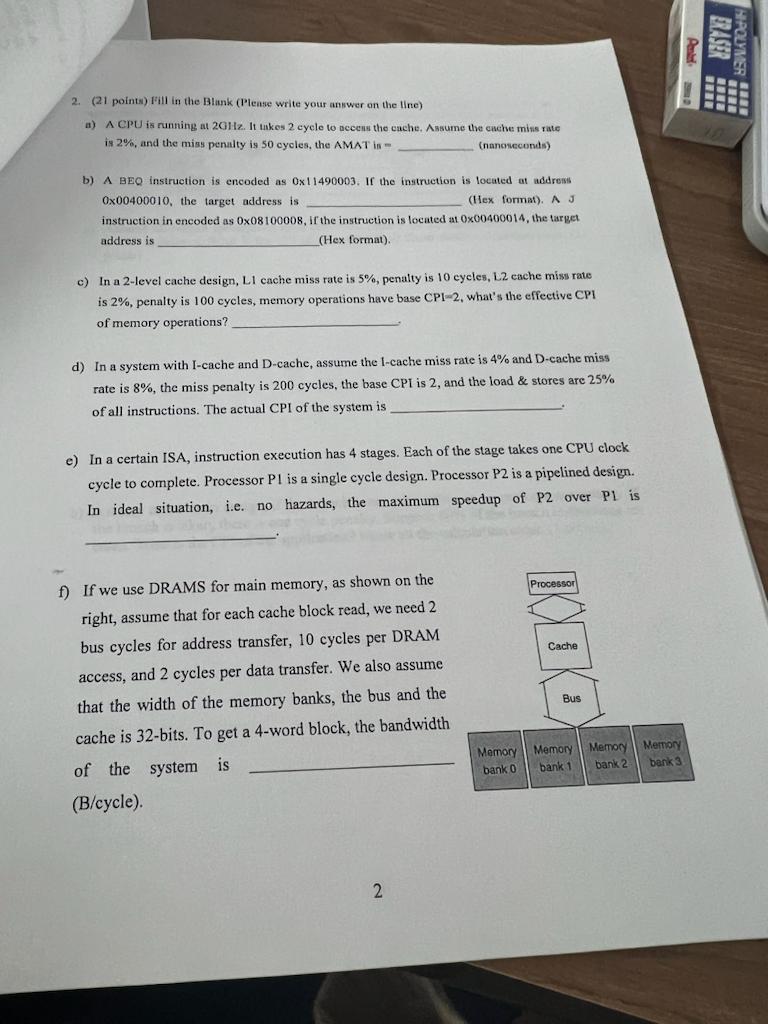

2. (21 points) fill in the Blunk (Please write your answer on the line) a) A CPU is running at 2GHz. It tikes 2 cycle to aceens the cache. Assume the cache mins rate is 2%, and the miss penalty is 50 cycles, the AMAT is = (nanchecunds) b) A BEQ instruction is encoded as 011490003. If the instruetion is located at address 000400010, the target address is (Hex format). A J instruction in encoded as 008100008, If the instruction is located at 000400014, the target address is . (Hex format). c) In a 2-level cache design, Ll cache miss rate is 5%, penalty is 10 cycles, LZ cache miss rate is 2%, penalty is 100 cycles, memory operations have base CPl 2 , what's the effective CPI of memory operations? d) In a system with I-cache and D-cache, assume the 1-cache miss rate is 4% and D-cache miss rate is 8%, the miss penalty is 200 cycles, the base CPI is 2 , and the load \& stores are 25% of all instructions. The actual CPI of the system is . e) In a certain ISA, instruction execution has 4 stages. Each of the stage takes one CPU clock cycle to complete. Processor P1 is a single cycle design. Processor P2 is a pipelined design. In ideal situation, i.e. no hazards, the maximum speedup of P2 over P1 is f) If we use DRAMS for main memory, as shown on the right, assume that for each cache block read, we need 2 bus cycles for address transfer, 10 cycles per DRAM access, and 2 cycles per data transfer. We also assume that the width of the memory banks, the bus and the cache is 32-bits. To get a 4-word block, the bandwidth of the system is (B/cycle)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts