Question: 2. Assume that the maximum delay through the components in the OTTER are as follows: PC= 2ns Memory (read)= 6ns Muxes = lns Register File

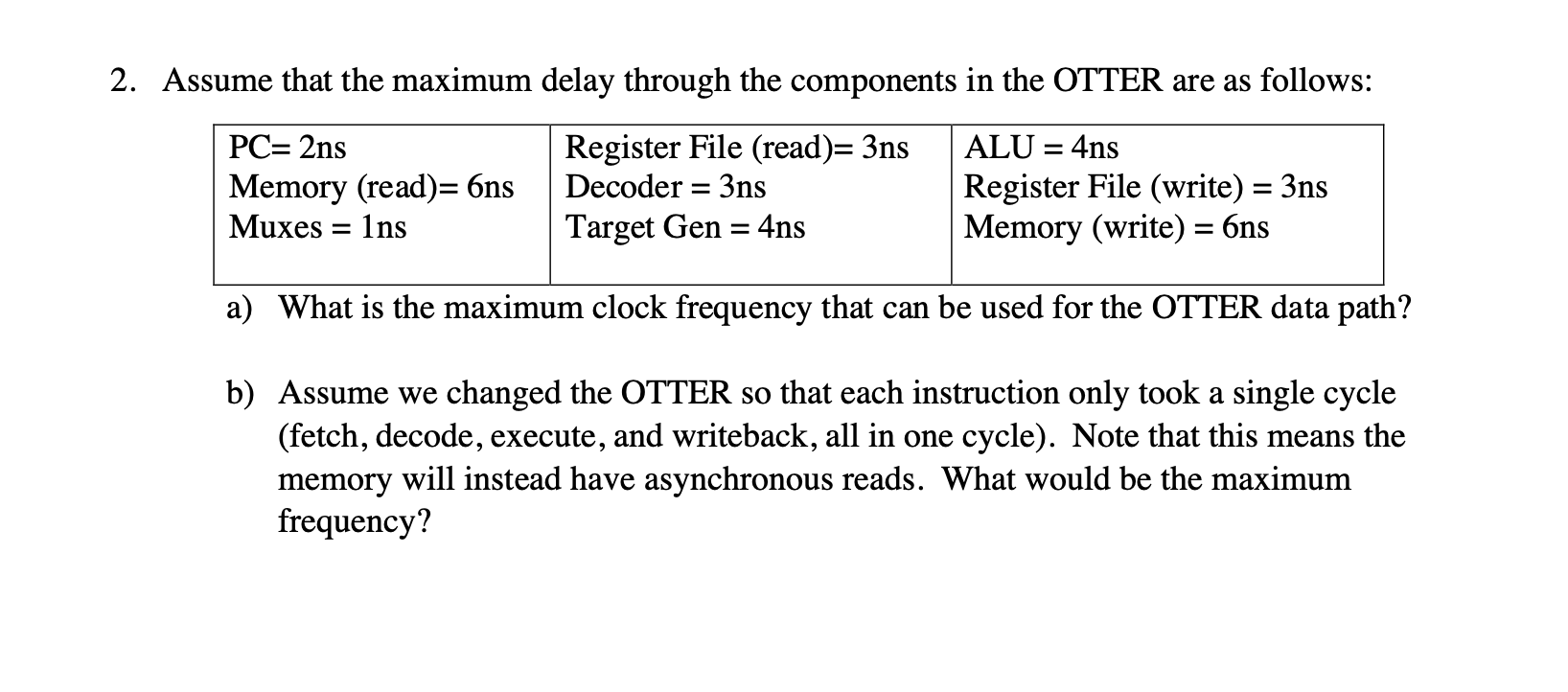

2. Assume that the maximum delay through the components in the OTTER are as follows: PC= 2ns Memory (read)= 6ns Muxes = lns Register File (read)= 3ns Decoder = 3ns Target Gen = 4ns ALU = 4ns Register File (write) = 3ns Memory (write) = 6ns a) What is the maximum clock frequency that can be used for the OTTER data path? b) Assume we changed the OTTER so that each instruction only took a single cycle (fetch, decode, execute, and writeback, all in one cycle). Note that this means the memory will instead have asynchronous reads. What would be the maximum frequency? 2. Assume that the maximum delay through the components in the OTTER are as follows: PC= 2ns Memory (read)= 6ns Muxes = lns Register File (read)= 3ns Decoder = 3ns Target Gen = 4ns ALU = 4ns Register File (write) = 3ns Memory (write) = 6ns a) What is the maximum clock frequency that can be used for the OTTER data path? b) Assume we changed the OTTER so that each instruction only took a single cycle (fetch, decode, execute, and writeback, all in one cycle). Note that this means the memory will instead have asynchronous reads. What would be the maximum frequency

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts