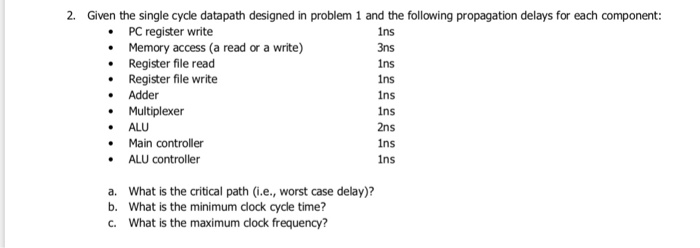

Question: 2. Given the single cycle datapath designed in problem 1 and the following propagation delays for each component PC register write ns 3ns ns Ins

2. Given the single cycle datapath designed in problem 1 and the following propagation delays for each component PC register write ns 3ns ns Ins 1ns 1ns 2ns 1ns 1ns .Memory access (a read or a write) .Register file read Register file write Adder .Multiplexer ALU Main controller ALU controller a. What is the critical path (i.e., worst case delay)? b. What is the minimum clock cycle time? c. What is the maximum clock frequency? 2. Given the single cycle datapath designed in problem 1 and the following propagation delays for each component PC register write ns 3ns ns Ins 1ns 1ns 2ns 1ns 1ns .Memory access (a read or a write) .Register file read Register file write Adder .Multiplexer ALU Main controller ALU controller a. What is the critical path (i.e., worst case delay)? b. What is the minimum clock cycle time? c. What is the maximum clock frequency

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts