Question: 2. (Based on COD 5.2) Caches are important to providing a high-performance memory hierarchy to processors. Below is a list of 32-bit memory address references.

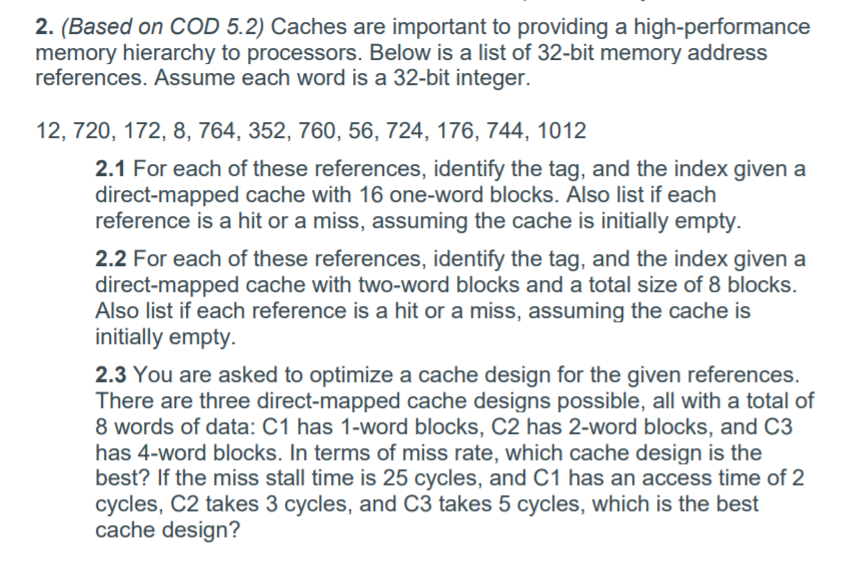

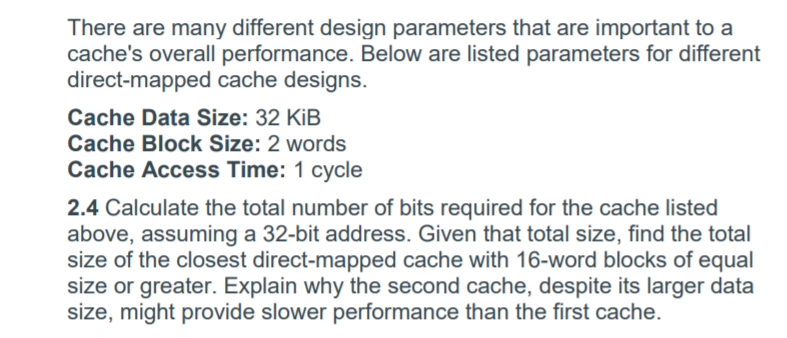

2. (Based on COD 5.2) Caches are important to providing a high-performance memory hierarchy to processors. Below is a list of 32-bit memory address references. Assume each word is a 32-bit integer. 12, 720, 172, 8, 764, 352, 760, 56, 724, 176, 744, 1012 2.1 For each of these references, identify the tag, and the index given a direct-mapped cache with 16 one-word blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty. 2.2 For each of these references, identify the tag, and the index given a direct-mapped cache with two-word blocks and a total size of 8 blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty 2.3 You are asked to optimize a cache design for the given references. There are three direct-mapped cache designs possible, all with a total of 8 words of data: C1 has 1-word blocks, C2 has 2-word blocks, and C3 has 4-word blocks. In terms of miss rate, which cache design is the best? If the miss stall time is 25 cycles, and C1 has an access time of 2 cycles, C2 takes 3 cycles, and C3 takes 5 cycles, which is the best cache design

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts