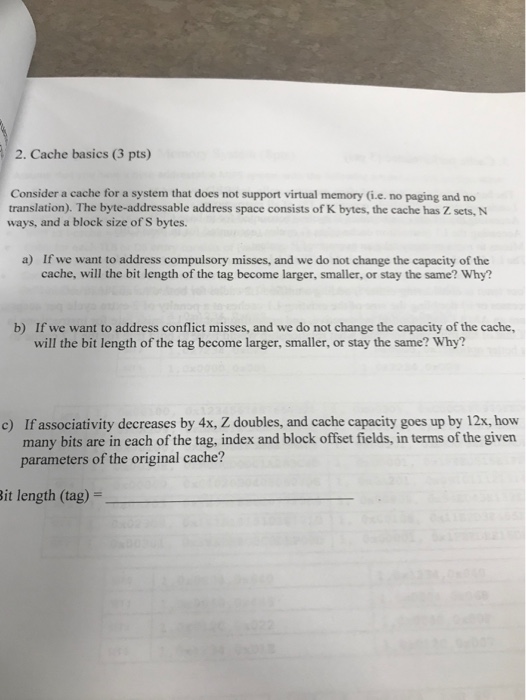

Question: 2. Cache basics (3 pts) Consider a cache for a system that does not support virtual memory Gi.e. no paging and no translation). The byte-addressable

2. Cache basics (3 pts) Consider a cache for a system that does not support virtual memory Gi.e. no paging and no translation). The byte-addressable address space consists of K bytes, the cache has Z sets, N ways, and a block size of S bytes. a) If we want to address compulsory misses, and we do not change the capacity of the cache, will the bit length of the tag become larger, smaller, or stay the same? Why? If we want to address conflict misses, and we do not change the capacity of the cache, will the bit length of the tag become larger, smaller, or stay the same? Why? b) If associativity decreases by 4x, Z doubles, and cache capacity goes up by 12x, how many bits are in each of the tag, index and block offset fields, in terms of the given parameters of the original cache? c) it length (tag)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts