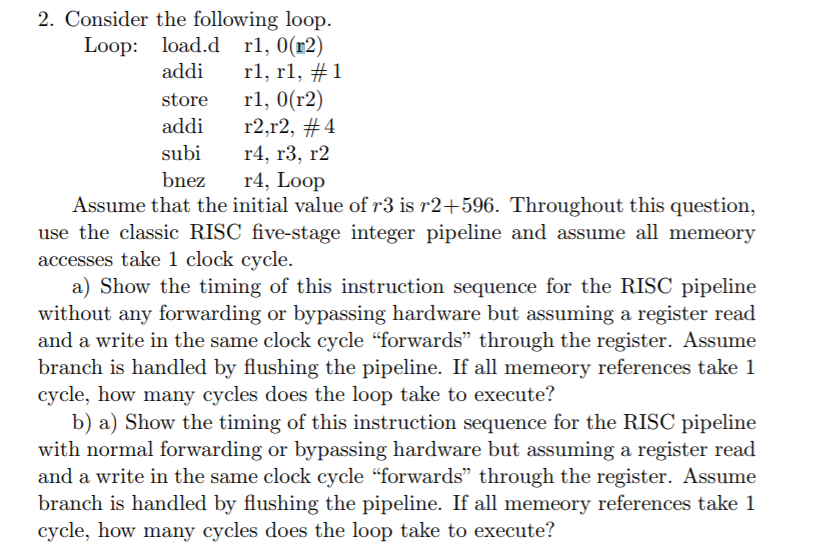

Question: 2. Consider the following loop Loop: load.d rl, 0(r2) addi r1, r1, #1 store rl, 0(r2) addi r2,r2, #4 subir4. r3, r2 bnez r4. Loop

2. Consider the following loop Loop: load.d rl, 0(r2) addi r1, r1, #1 store rl, 0(r2) addi r2,r2, #4 subir4. r3, r2 bnez r4. Loop Assume that the initial value of r3 is r2+596. Throughout this question, use the classic RISC five-stage integer pipeline and assume all memeory accesses take 1 clock cycle. a) Show the timing of this instruction sequence for the RISC pipeline without any forwarding or bypassing hardware but assuming a register read and a write in the same clock cycle "forwards" through the register. Assume branch is handled by flushing the pipeline. If all memeory references take 1 cycle, how many cycles does the loop take to execute? b) a) Show the timing of this instruction sequence for the RISC pipeline with normal forwarding or bypassing hardware but assuming a register read and a write in the same clock cycle "forwards" through the register. Assume branch is handled by flushing the pipeline. If all memeory references take 1 cycle, how many cycles does the loop take to execute

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts