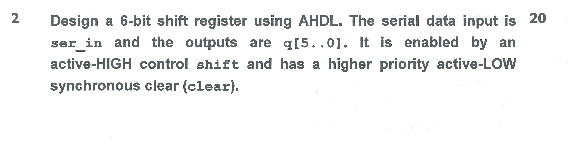

Question: 2 Design a 6-bit shift register using AHDL. The serial data input is 20 ser_in and the outputs are q[5.,0]. It is enabled by an

2 Design a 6-bit shift register using AHDL. The serial data input is 20 ser_in and the outputs are q[5.,0]. It is enabled by an active-HIGH control shift and has a higher priority active-LOW synchronous clear (clear). 2 Design a 6-bit shift register using AHDL. The serial data input is 20 ser_in and the outputs are q[5.,0]. It is enabled by an active-HIGH control shift and has a higher priority active-LOW synchronous clear (clear)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts