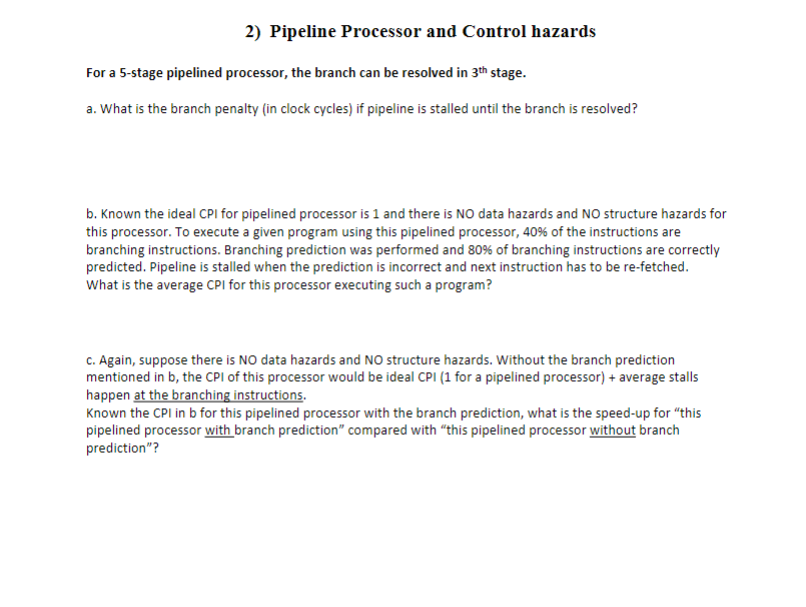

Question: 2 ) Pipeline Processor and Control hazards For a 5 - stage pipelined processor, the branch can be resolved in ( 3 ^ {

Pipeline Processor and Control hazards

For a stage pipelined processor, the branch can be resolved in text th stage.

a What is the branch penalty in clock cycles if pipeline is stalled until the branch is resolved?

b Known the ideal CPI for pipelined processor is and there is NO data hazards and NO structure hazards for this processor. To execute a given program using this pipelined processor, of the instructions are branching instructions. Branching prediction was performed and of branching instructions are correctly predicted. Pipeline is stalled when the prediction is incorrect and next instruction has to be refetched. What is the average CPI for this processor executing such a program?

c Again, suppose there is NO data hazards and NO structure hazards. Without the branch prediction mentioned in b the CPI of this processor would be ideal CPI for a pipelined processor average stalls happen at the branching instructions.

Known the CPI in b for this pipelined processor with the branch prediction, what is the speedup for "this pipelined processor with branch prediction" compared with "this pipelined processor without branch prediction"?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock