Question: 2.6 Digital Lock Design with Hardcoded Password: By modifying the parallel load register de of logic values that cannot be changed. Such passwords can be

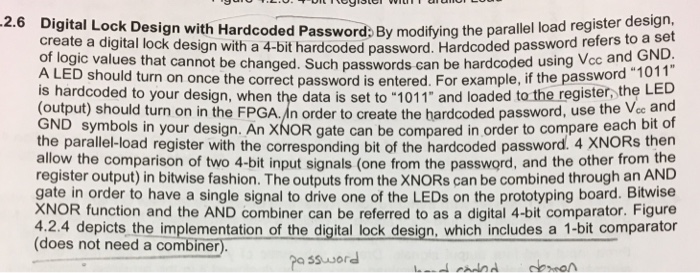

2.6 Digital Lock Design with Hardcoded Password: By modifying the parallel load register de of logic values that cannot be changed. Such passwords can be hardcoded using Vcc and create a digital lock design with a 4-bit hardcoded password. Hardcoded password refers to a se 5 A LED should turn on once the correct password is entered. For example, if the passwor d "1011 is hardcoded to your design, when the data is set to "1011" and loaded to the register,the LED output) should turn on in the FPGA.An order to create the hardcoded password, use the Vce and GND symbols in your design. An XNOR gate can be compared in order to compare each bit of the parallel-load register with the corresponding bit of the hardcoded password. 4 XNORs then allow the comparison of two 4-bit input signals (one from the password, and the other from the register output) in bitwise fashion. The outputs from the XNORs can be combined through an AND gate in order to have a single signal to drive one of the LEDs on the prototyping board. Bitwise XNOR function and the AND combiner can be referred to as a digital 4-bit comparator. Figure 4.2.4 depicts the implementation of the digital lock design, which includes a 1-bit comparator (does not need a combiner) ra 5

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts