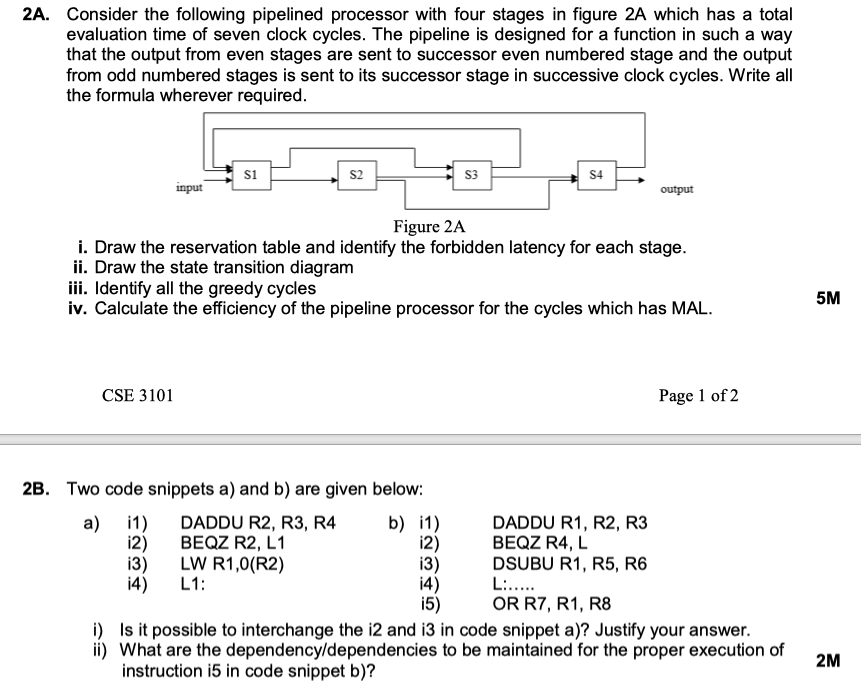

Question: 2A. Consider the following pipelined processor with four stages in figure 2A which has a total evaluation time of seven clock cycles. The pipeline is

2A. Consider the following pipelined processor with four stages in figure 2A which has a total evaluation time of seven clock cycles. The pipeline is designed for a function in such a way that the output from even stages are sent to successor even numbered stage and the output from odd numbered stages is sent to its successor stage in successive clock cycles. Write all the formula wherever required S1 S2 S3 S4 input output Figure 2A i. Draw the reservation table and identify the forbidden latency for each stage ii. Draw the state transition diagram iii. ldentify all the greedy cycles iv. Calculate the efficiency of the pipeline processor for the cycles which has MAL 5M CSE 3101 Page 1 of 2 2B. Two code snippets a) and b) are given below a) l) 2) BEQZ R2, L1 i3) LW R1,0(R2) 4) L1: DADDU R2, R3, R4 b) il) 2) BEQZ R4, L 3)DSUBU R1, R5, R6 DADDU R1,R2, R3 L: i5)OR R7, R1, R8 i) Is it possible to interchange the i2 and i3 in code snippet a)? Justify your answer. ii) What are the dependency/dependencies to be maintained for the proper execution of 2M instruction i5 in code snippet b)? 2A. Consider the following pipelined processor with four stages in figure 2A which has a total evaluation time of seven clock cycles. The pipeline is designed for a function in such a way that the output from even stages are sent to successor even numbered stage and the output from odd numbered stages is sent to its successor stage in successive clock cycles. Write all the formula wherever required S1 S2 S3 S4 input output Figure 2A i. Draw the reservation table and identify the forbidden latency for each stage ii. Draw the state transition diagram iii. ldentify all the greedy cycles iv. Calculate the efficiency of the pipeline processor for the cycles which has MAL 5M CSE 3101 Page 1 of 2 2B. Two code snippets a) and b) are given below a) l) 2) BEQZ R2, L1 i3) LW R1,0(R2) 4) L1: DADDU R2, R3, R4 b) il) 2) BEQZ R4, L 3)DSUBU R1, R5, R6 DADDU R1,R2, R3 L: i5)OR R7, R1, R8 i) Is it possible to interchange the i2 and i3 in code snippet a)? Justify your answer. ii) What are the dependency/dependencies to be maintained for the proper execution of 2M instruction i5 in code snippet b)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts